## EECS 312: Digital Integrated Circuits Final Exam

## 23 April 2009

#### Robert Dick

Show your work. Derivations are required for credit; end results are insufficient. Closed book. You may use a calculator.

Honor Pledge: I have neither given nor received aid in this exam.

Signature:

- 1. (10 pts.)  $k_n = \frac{W\mu_n\epsilon_{ox}}{Lt_{ox}}$  When the move from SiO<sub>2</sub> to high- $\kappa$  gate dielectric occurred, what qualitative changes were made to the variables upon which  $k_n$  depends? You may assume that  $k_n$  remains fixed. Use only a few sentence fragments for your answer.

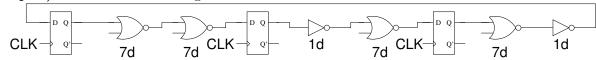

- 2. (10 pts.) Consider the following circuit:

The numbers near the logic gates indicate delays. Disconnected logic gate inputs may be assumed to be stable. Draw the gate- and latch-level diagram of a two-phase latch-based reimplementation of this circuit and indicate the minimal safe clock period. Do not change anything but the positions of the latches. You may neglect latch delays.

- 3. (10 pts.) Indicate two ways of programming floating-gate transistors and two ways of erasing floating-gate transistors. It is fine for the methods to require slightly different floating gate transistor designs. Use at most four short phrases.

- (10 pts.) Draw the transistor-level diagram for a sense amplifier that reprograms the read value. Your circuit should have the following inputs: *read-program*, *equalize*, *bit*, and *bit*. You may not assume access to complemented input literals.

- 5. (10 pts.) Draw a gate-level diagram for a three-bit carry-lookahead adder. Correctness counts the most, but efficiency also counts. You may use hierarchy. In other words, once you show how to construct something more complex than a standard logic gate, you can assign a symbol to it and reuse that symbol.

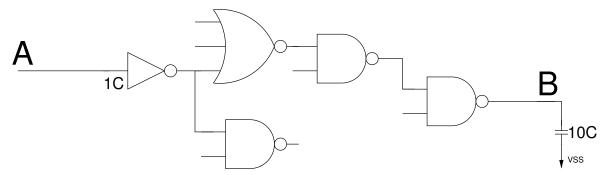

- 6. (10 pts.) Use the concept of logical effort to size the gates in the following circuit to minimize the delay for path  $A \rightarrow B$ .

You need not round your sizes.

- 7. (10 pts.) Draw a transistor-level diagram of a 3:8 decoder in which the transistors are sized to achieve the same output resistance to ground and  $V_{DD}$  as an inverter with gate capacitance 3C.

- 8. (10 pts.) Draw the gate-level diagram of a rising edge triggered scan-flop, i.e., a flip-flop that can be used to support normal operation and scan-chain testing. You may use transistors in addition to logic gates. If sizing is essential for correct operation, label the appropriate gates and/or transistors as "narrow" and "wide".

- 9. (10 pts.) Determine the worst-case delay from precharge disable to output transition for a single-bit cell in a four-word MOS NAND ROM.  $\lambda = 125 \text{ nm}$ . All gates are  $2\lambda$  long and  $4\lambda$  wide. Sources and drains are  $3\lambda$  long and  $4\lambda$  wide. Assume (1) a default 0.25 µm process, (2) all inputs experiences a perfect step voltage change, and (3) an output capacitance of 10 fF.

|      | C <sub>OX</sub>                  | $C_O$        | $C_j$                            | $m_j$ | $\phi_b$ | $C_{jsw}$                      | $m_{jsw}$ | $\phi_{bsw}$ |

|------|----------------------------------|--------------|----------------------------------|-------|----------|--------------------------------|-----------|--------------|

|      | $(\mathrm{fF}/\mathrm{\mu m}^2)$ | $(fF/\mu m)$ | $(\mathrm{fF}/\mathrm{\mu m}^2)$ |       | (V)      | $(\mathrm{fF}/\mathrm{\mu m})$ |           | (V)          |

| NMOS | 6                                | 0.31         | 2                                | 0.5   | 0.9      | 0.28                           | 0.44      | 0.9          |

| PMOS | 6                                | 0.27         | 1.9                              | 0.48  | 0.9      | 0.22                           | 0.32      | 0.9          |

# MODELS FOR CMOS DEVICES

| CMOS (0.25 µm) – Unified Mode | el. |

|-------------------------------|-----|

|-------------------------------|-----|

|      | V <sub>70</sub> (V) | γ (V <sup>0.5</sup> ) | $V_{DSAT}$ (V) | k' (A/V <sup>2</sup> ) | $\lambda$ (V <sup>-1</sup> ) |

|------|---------------------|-----------------------|----------------|------------------------|------------------------------|

| NMOS | 0.43                | 0.4                   | 0.63           | 115 × 10 <sup>-6</sup> | 0.06                         |

| PMOS | -0.4                | -0.4                  | -1             | -30 × 10 <sup>-6</sup> | -0.1                         |

CMOS (0.25  $\mu$ m) – Switch Model ( $R_{eq}$ )

| $V_{DD}(\mathbf{V})$ | 1    | 1.5 | 2  | 2.5 |

|----------------------|------|-----|----|-----|

| NMOS (kΩ)            | · 35 | 19  | 15 | 13  |

| PMOS (kΩ)            | 115  | 55  | 38 | 31  |

### CMOS (0.25 µm) - BSIM Model

See Website: http://bwrc.eecs.berkeley.edu/IcBook

# VALUES OF MATERIAL AND PHYSICAL CONSTANTS

| Name                                                                  | Symbol                | Value                  | Units                       |

|-----------------------------------------------------------------------|-----------------------|------------------------|-----------------------------|

| Room temperature                                                      | <b>7</b> .            | 300 (= 27°C)           | к                           |

| Boltzman constant                                                     | k                     | $1.38 \times 10^{-23}$ | J/K                         |

| Electron charge                                                       | 4                     | $1.6 \times 10^{-19}$  | С                           |

| Thermal voltage                                                       | $\phi_r = kT/q$       | 26                     | mV (at 300 K)               |

| Intrinsic Carrier<br>Concentration (Silicon)                          | n <sub>i</sub>        | $1.5 \times 10^{10}$   | cm <sup>-3</sup> (at 300 K) |

| Permittivity of Si                                                    | <b>C</b> ,,           | $1.05 \times 10^{-12}$ | F/cm                        |

| Permittivity of SiO2                                                  | E <sub>0x</sub>       | $3.5 \times 10^{-13}$  | F/cm                        |

| Resistivity of Al                                                     | ρ <sub>ΑΙ</sub>       | $2.7 \times 10^{-8}$   | Ω-m                         |

| Resistivity of Cu                                                     | Peu                   | $1.7 \times 10^{-8}$   | <b>Ω-</b> m                 |

| Magnetic permeability<br>of vacuum<br>(similar for SiO <sub>2</sub> ) | μο                    | $12.6 \times 10^{-7}$  | Wb/Am                       |

| Speed of light<br>(in vacuum)                                         | <i>c</i> <sub>0</sub> | 30                     | cm/nsec                     |

| Speed of light (in $SiO_2$ )                                          | G <sub>ex</sub>       | 15                     | cm/nsec                     |

# FORMULAS AND EQUATIONS

• •

#### Diode

$$I_{D} = I_{S}(e^{V_{D}/\Phi_{T}} - 1) = Q_{D}/\tau_{T}$$

$$C_{j} = \frac{C_{j0}}{(1 - V_{D}/\Phi_{0})^{m}}$$

$$K_{eq} = \frac{-\Phi_{0}^{m}}{(V_{high} - V_{low})(1 - m)} \times [(\Phi_{0} - V_{high})^{1 - m} - (\Phi_{0} - V_{low})^{1 - m}]$$

#### **MOS Transistor**

$$V_T = V_{T0} + \gamma(\sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|-2\phi_F|})$$

$$I_D = \frac{k'_n W}{2} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \text{ (sat)}$$

$$I_D = v_{sat} C_{os} W \left( V_{GS} - V_T - \frac{V_{DSAT}}{2} \right) (1 + \lambda V_{DS}) \text{ (velocity sat)}$$

$$I_D = k'_n \frac{W}{L} \left( (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right) \text{ (triode)}$$

$$\frac{v_{GS}}{2} \left( (V_{GS} - V_T) V_{DS} - \frac{v_{DS}^2}{2} \right) \text{ (triode)}$$

$$I_D = I_S e^{\overline{nkT/q}} \left( 1 - e^{-\overline{kT/q}} \right)$$

(subthreshold)

#### Deep Submicron MOS Unified Model

$$\begin{split} I_D &= 0 \text{ for } V_{GT} \leq 0 \\ I_D &= k' \frac{W}{L} \left( V_{GT} V_{min} - \frac{V_{min}^2}{2} \right) (1 + \lambda V_{DS}) \text{ for } V_{GT} \geq 0 \\ \text{with } V_{min} &= \min(V_{GT}, V_{DS}, V_{DSAT}) \\ \text{and } V_{GT} &= V_{GS} - V_T \end{split}$$

#### MOS Switch Model

$$\begin{split} R_{eq} &= \frac{1}{2} \Big( \frac{V_{DD}}{I_{DSAT}(1 + \lambda V_{DD})} + \frac{V_{DD}/2}{I_{DSAT}(1 + \lambda V_{DD}/2)} \Big) \\ &\approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \Big( 1 - \frac{5}{6} \lambda V_{DD} \Big) \end{split}$$

#### Inverter

$$\begin{split} V_{OH} &= f(V_{OL}) \\ V_{OL} &= f(V_{OH}) \\ V_{M} &= f(V_{M}) \\ t_{p} &= 0.69 R_{eq} C_{L} = \frac{C_{L}(V_{swing}/2)}{I_{avg}} \\ P_{dyn} &= C_{L} V_{DD} V_{swing} f \\ P_{stat} &= V_{DD} I_{DD} \end{split}$$

#### Static CMOS Inverter

$$\begin{split} V_{OH} &= V_{DD} \\ V_{OL} &= GND \\ V_{M} &\approx \frac{rV_{DD}}{1+r} \quad \text{with} \quad r = \frac{k_{p}V_{DSATp}}{k_{n}V_{DSATn}} \\ V_{IH} &= V_{M} - \frac{V_{M}}{g} \qquad V_{IL} = V_{M} + \frac{V_{DD} - V_{M}}{g} \\ \text{with } g &= \frac{1+r}{(V_{M} - V_{Tn} - V_{DSATn}/2)(\lambda_{n} - \lambda_{p})} \\ t_{p} &= \frac{t_{pHL} + t_{pLH}}{2} = 0.69 C_{L} \Big( \frac{R_{eqn} + R_{eqp}}{2} \Big) \\ P_{av} &= C_{L}V_{DD}^{2}f \end{split}$$

## Interconnect Lumped RC: $t_p = 0.69 RC$ Distributed RC: $t_p = 0.38 RC$ RC-chain:

$$\tau_N = \sum_{i=1}^N R_i \sum_{j=i}^N C_j = \sum_{i=1}^N C_i \sum_{j=1}^i R_j$$

Transmission line reflection:

$$\rho = \frac{V_{refl}}{V_{inc}} = \frac{I_{refl}}{I_{inc}} = \frac{R - Z_0}{R + Z_o}$$

# CMOS COMBINATIONAL LOGIC

**Transistor Sizing using Logical Effort**

$$F = \frac{C_L}{C_{g1}} = \prod_1^N \frac{f_1}{b_1} \qquad G = \prod_1^N g_1 \qquad D = t_{p0} \sum_{j=1}^N \left( p_j + \frac{f_j g_j}{\gamma} \right)$$

$$B = \prod_1^N b_1 \qquad H = FGB \qquad D_{min} = t_{p0} \left( \sum_{j=1}^N p_j + \frac{N(\frac{N}{\sqrt{H}})}{\gamma} \right)$$