### EECS 312: Digital Integrated Circuits Midterm Exam Solutions

#### 12 March 2009

#### Robert Dick

Show your work. Derivations are required for credit; end results are insufficient.

Closed book. No electronic mental aids.

Honor Pledge: I have neither given nor received aid in this exam.

Signature:

1. (5 pts.)  $k_n = \frac{W\mu_n\epsilon_{ox}}{Lt_{ox}}$  When the move from SiO<sub>2</sub> to high- $\kappa$  gate dielectric occurred, what qualitative changes were made to the variables upon which  $k_n$  depends? Use only a few sentence fragments for your answer.

$$\epsilon_{ox} \uparrow, t_{ox} \uparrow$$

.

Note: If you didn't get this one, please read the Spectrum article. It is a very fun article!

2. (10 pts.) Consider a static CMOS gate implementing the following function:

$$f(a, b, c) = ab + \overline{b}c$$

This gate is subjected to the following transition  $a = 1, b = 0, c = 1 \rightarrow a = 1, b = 1, c = 1$ . Will the gate's dynamic energy consumption be greater if its inputs come from other standard static CMOS gates and inverters, or from DCVSL gates? Use one sentence to explain why. You may also use a schematic if that makes your answer clearer.

Any answer expressing the possible relationship between different transition times for b and  $\bar{b}$  when implemented using standard static CMOS gates and inverters, but not for DCVSL, and output glitching for f received credit. With DCVSL, the two will change at approximately the same time. With standard static CMOS gates and inverters, one will switch significantly before the other (plus the delay of an inverter). If b switches before  $\bar{b}$ , this will cause the output of f to briefly glitch to 0.

Note: Do not be very concerned if you did not have this answer: few did. In retrospect, I believe I wrote this question badly. I will give more details on such potentially-ambiguous questions in future exams.

3. (10 pts.) Given process variation resulting in a Gaussian distribution of threshold voltage around its nominal value, will total integrated circuit sub-threshold leakage power consumption be higher, the same, or lower than that of an integrated circuit in which all transistors have nominal threshold voltages? Use at most two sentences to explain why.

Total leakage is likely to be higher. Leakage power is proportional to  $e^{\frac{-\Delta V_T}{nkT/q}}$ . Thus a given decrease in  $V_T$  results in a big increase in leakage power while the same increase in  $V_T$  results in a small decrease in leakage power.

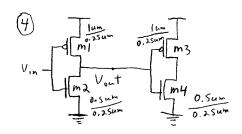

4. (10 pts.) Determine the high-to-low propagation delay for an inverter with a 500 nm wide NMOSFET and a 1 µm wide PMOSFET with its output connected to another identical inverter. Assume the default 250 nm process. Do consider overlap capacitance. Recall that it is necessary to consider both bottom and sidewall capacitance. You may neglect the resistance and capacitance of the wire connecting the two inverters. Note that the switch model reference table gives values for W/L = transistors. Show your work.

Find to HL for Vout

Vdd = 2.5V

toHL = RnCL

Rn is Reg of M2 For nmos W=L=0:25um, Reg = 13ks For W= 0.5um, Reg = 6.5ks

CL is composed of gate-channel and overlap cap for the second inverter (m3 and m4) and drain-junction and gate-drain cap for the second inverter (m1 and m2).

$C_{9Cm3} = C_{0x_p}WL = 6.1.0.25 = 0.5 fF$   $C_{overlap m3} = C_{aso} + C_{abo} = 2.C_{op}W = 2.0.27.1 = 0.54 fF$   $C_{9Cm4} = C_{0x_p}WL = 6.0.5.0.25 = 0.75 fF$   $C_{9Cm4} = C_{0x_p}WL = 6.0.5.0.25 = 0.75 fF$  $C_{9Cm4} = C_{0x_p}WL = 6.0.5.0.25 = 0.31.0.5 = 0.31 fF$

Cgdm1 = Cop W = 0.27.1 = 0.27fF

Miller effect: Convert to cap to ground

Cgd;= 2. Cgdm1

= 0.54 fF

Cgdm2 = Con W = 0.31.0.5 = 0.155 fF

Miller Effect

Cgdx=2. Cgdm2

= 0.31 fF

5. (10 pts.) Assuming the default 250 nm process, determine the minimum and maximum percentage change in subthreshold leakage current of a minimal-width NMOSFET given that the threshold voltage may deviate by 0.1 V from the nominal in either direction. You may assume that n = 1.5.

Let

$$\sigma = 1 - e^{-\frac{V_{DS}}{kT/q}}$$

(1)

$$I_D^{nominal} = I_S e^{\frac{V_{GS}}{nkT/q}} \sigma \tag{2}$$

$$I_D^{nominal} = I_S e^{\frac{0 \text{ V}}{1.5 \cdot 26 \text{ mV}}} \sigma \qquad \text{(from table)} \qquad (3)$$

$$I_D^{nominal} = I_S e^{25.6 \cdot 0} \sigma \tag{4}$$

$$I_D^{nominal} = I_S \sigma \tag{5}$$

$$I_D^{low} = I_S e^{25.6 \cdot -0.1} \sigma$$

(6)

$$I_D^{low} = I_S e^{-2.56} \sigma \tag{7}$$

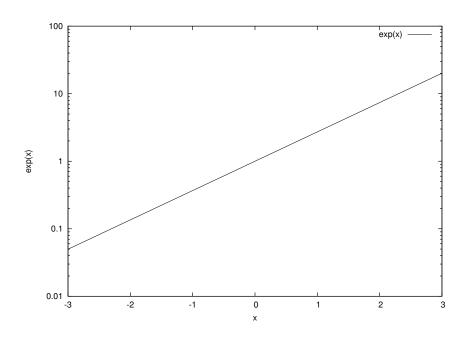

$$I_D^{low} = I_S \cdot 0.0773 \cdot \sigma \tag{from plot}$$

$$I_D^{high} = I_S e^{25.6 \cdot 0.1} \sigma \tag{9}$$

$$I_D^{high} = I_S e^{2.56} \sigma \tag{10}$$

$$I_D^{high} = I_S \cdot 12.9 \cdot \sigma$$

(from plot) (11)

$$\Delta I_D^{low} = \frac{I_D^{low} - I_D^{nominal}}{I_D^{nominal}} \tag{12}$$

$$\Delta I_D^{low} = \frac{I_S \cdot 0.0773 \cdot \sigma - I_S \sigma}{I_S \sigma} \tag{13}$$

$$\Delta I_D^{low} = 0.0773 - 1 = -0.923 = -92.3\% \tag{14}$$

$$\Delta I_D^{low} = 0.0773 - 1 = -0.923 = -92.3\%$$

$$\Delta I_D^{high} = \frac{I_D^{high} - I_D^{nominal}}{I_D^{nominal}}$$

(15)

$$\Delta I_D^{high} = \frac{I_S \cdot 12.9 \cdot \sigma - I_S \sigma}{I_S \sigma} \tag{16}$$

$$\Delta I_D^{high} = 12.9 - 1 = 11.9 = 1190\% \tag{17}$$

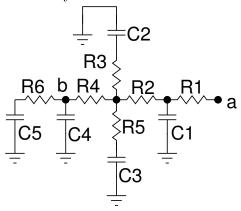

6. (10 pts.) Determine the Elmore delay from Node a to Node b in the following circuit.

$$\tau_{ab} = R1(C1 + C2 + C3 + C4 + C5) + R2(C2 + C3 + C4 + C5) + R4(C4 + C5)$$

(18)

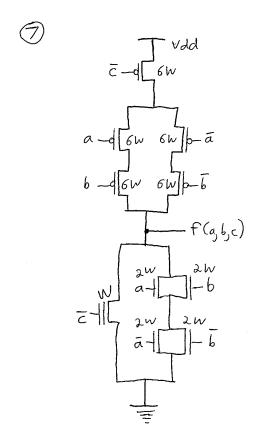

7. (10 pts.) Show the circuit diagram for a static CMOS implementation of the following function sized to have the same resistance to ground and  $V_{DD}$  as an inverter with a W wide NMOSFET and an 2W wide PMOSFET. You may assume access to complemented and uncomplemented input literals, i.e., a and  $\bar{a}$ .

$$f(a, b, c) = (ab + \overline{a}\,\overline{b})c$$

8. (0 pts.) Was this exam  $\square$  tricky and surprising or did it  $\square$  fairly closely follow the material we focused on in class?

Note: Problem 2 was trickier than I intended it to be, and I intend to be clearer in the future. Problem 4 was somewhat tedious, but you shouldn't be surprised to see a tedious problem again in the future.

|      | $C_{OX}$ (fF/ $\mu$ m <sup>2</sup> ) | $C_O$ (fF/ $\mu$ m) | $C_j$ (fF/ $\mu$ m <sup>2</sup> ) | $m_{j}$ | $\phi_b$ (V) | $C_{jsw}$ (fF/ $\mu$ m) | $m_{jsw}$ | $\phi_{bsw}$ (V) |

|------|--------------------------------------|---------------------|-----------------------------------|---------|--------------|-------------------------|-----------|------------------|

| NMOS | 6                                    | 0.31                | 2                                 | 0.5     | 0.9          | 0.28                    | 0.44      | 0.9              |

| PMOS | 6                                    | 0.27                | 1.9                               | 0.48    | 0.9          | 0.22                    | 0.32      | 0.9              |

# MODELS FOR CMOS DEVICES

CMOS (0.25  $\mu$ m) – Unified Model.

|      | V <sub>70</sub> (V) | γ(V <sup>0.5</sup> ) | V <sub>DSAT</sub> (V) | k' (A/V²)              | λ (V <sup>-1</sup> ) |

|------|---------------------|----------------------|-----------------------|------------------------|----------------------|

| NMOS | 0.43                | 0.4                  | 0.63                  | 115 × 10 <sup>-6</sup> | 0.06                 |

| PMOS | -0.4                | -0.4                 | -1                    | -30 × 10 <sup>-6</sup> | -0.1                 |

CMOS (0.25  $\mu$ m) – Switch Model ( $R_{eq}$ )

| $V_{DD}(\mathbf{V})$ | 1    | 1.5 | 2  | 2.5 |

|----------------------|------|-----|----|-----|

| NMOS (kΩ)            | . 35 | 19  | 15 | 13  |

| PMOS (kΩ)            | 115  | 55  | 38 | 31  |

CMOS (0.25  $\mu m$ ) – BSIM Model

See Website: http://bwrc.eecs.berkeley.edu/IcBook

# VALUES OF MATERIAL AND PHYSICAL CONSTANTS

| Name                                                                  | Symbol          | Value                  | Units                       |

|-----------------------------------------------------------------------|-----------------|------------------------|-----------------------------|

| Room temperature                                                      | γ.              | 300 (= 27°C)           | к                           |

| Boltzman constant                                                     | k               | $1.38 \times 10^{-23}$ | J/K                         |

| Electron charge                                                       | q               | $1.6 \times 10^{-19}$  | С                           |

| Thormal voltage                                                       | $\phi_T = kT/q$ | 26                     | mV (at 300 K)               |

| Intrinsic Carrier Concentration (Silicon)                             | $n_{i}$         | $1.5\times10^{10}$     | cm <sup>-3</sup> (at 300 K) |

| Permittivity of Si                                                    | <b>c</b> ,,     | $1.05 \times 10^{-12}$ | F/cm                        |

| Permittivity of SiO <sub>2</sub>                                      | <b>4</b> 0,1    | $3.5 \times 10^{-13}$  | F/cm                        |

| Resistivity of Al                                                     | PAI             | $2.7 \times 10^{-8}$   | Ω-m                         |

| Resistivity of Cu                                                     | Pa              | $1.7 \times 10^{-8}$   | Ω-m                         |

| Magnetic permeability<br>of vacuum<br>(similar for SiO <sub>2</sub> ) | $\mu_0$         | $12.6 \times 10^{-7}$  | Wb/Am                       |

| Speed of light $c_0$ (in vacuum)                                      |                 | 30                     | cm/nsec                     |

| Speed of light (in SiO <sub>2</sub> )                                 | $c_{ex}$        | 15                     | cm/nsec                     |

## FORMULAS AND EQUATIONS

#### Diode

$$\begin{split} I_D &= I_S(e^{V_D/\Phi_T} - 1) = Q_D/\tau_T \\ C_j &= \frac{C_{j0}}{(1 - V_D/\Phi_0)^m} \\ K_{eq} &= \frac{-\Phi_0^n}{(V_{high} - V_{low})(1 - m)} \times \\ & [(\Phi_0 - V_{high})^{1 - m} - (\Phi_0 - V_{low})^{1 - m}] \end{split}$$

#### **MOS Transistor**

$$\begin{split} V_T &= V_{T0} + \gamma (\sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|-2\phi_F|}) \\ I_D &= \frac{k_n W}{2 L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \text{ (sat)} \\ I_D &= v_{sat} C_{ox} W \bigg( V_{GS} - V_T - \frac{V_{DSAT}}{2} \bigg) (1 + \lambda V_{DS}) \\ & \text{ (velocity sat)} \end{split}$$

$$\begin{split} I_D &= k_n' \frac{W}{L} \Big( (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \Big) \text{ (triode)} \\ I_D &= I_S e^{\frac{V_{GS}}{nKT/q}} \Big( 1 - e^{-\frac{V_{DS}}{kT/q}} \Big) \text{ (subthreshold)} \end{split}$$

#### Deep Submicron MOS Unified Model

$$\begin{split} I_D &= 0 \text{ for } V_{GT} \leq 0 \\ I_D &= k' \frac{W}{L} \bigg( V_{GT} V_{min} - \frac{V_{min}^2}{2} \bigg) (1 + \lambda V_{DS}) \text{ for } V_{GT} \geq 0 \\ \text{with } V_{min} &= \min(V_{GT}, V_{DS}, V_{DSAT}) \\ \text{and } V_{GT} &= V_{GS} - V_T \end{split}$$

#### MOS Switch Model

$$\begin{split} R_{eq} &= \frac{1}{2} \bigg( \frac{V_{DD}}{I_{DSAT} (1 + \lambda V_{DD})} + \frac{V_{DD} / 2}{I_{DSAT} (1 + \lambda V_{DD} / 2)} \bigg) \\ &\approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \bigg( 1 - \frac{5}{6} \lambda V_{DD} \bigg) \end{split}$$

#### Inverter

$$\begin{split} &V_{OH} = f(V_{OL}) \\ &V_{OL} = f(V_{OH}) \\ &V_{M} = f(V_{M}) \\ &I_{p} = 0.69 R_{eq} C_{L} = \frac{C_{L}(V_{swing}/2)}{I_{avg}} \\ &P_{dyn} = C_{L} V_{DD} V_{swing} f \\ &P_{stat} = V_{DD} I_{DD} \end{split}$$

#### **Static CMOS Inverter**

$$\begin{split} &V_{OH} = V_{DD} \\ &V_{OL} = GND \\ &V_{M} \approx \frac{rV_{DD}}{1+r} \quad \text{with} \quad r = \frac{k_{p}V_{DSATp}}{k_{n}V_{DSATn}} \\ &V_{IH} = V_{M} - \frac{V_{M}}{g} \qquad V_{IL} = V_{M} + \frac{V_{DD} - V_{M}}{g} \\ &\text{with } g \approx \frac{1+r}{(V_{M} - V_{Tn} - V_{DSATn}/2)(\lambda_{n} - \lambda_{p})} \\ &t_{p} = \frac{t_{pHL} + t_{pLH}}{2} = 0.69C_{L} \Big(\frac{R_{eqn} + R_{eqp}}{2}\Big) \\ &P_{av} = C_{L}V_{DD}^{2}f \end{split}$$

#### Interconnect

Lumped RC:  $t_p = 0.69 RC$ Distributed RC:  $t_p = 0.38 RC$

$$\tau_N = \sum_{i=1}^{N} R_i \sum_{j=i}^{N} C_j = \sum_{i=1}^{N} C_i \sum_{j=1}^{i} R_j$$

transmission line reflection:

$$\rho = \frac{V_{refl}}{V_{inc}} = \frac{I_{refl}}{I_{inc}} = \frac{R - Z_0}{R + Z_o}$$

## CMOS COMBINATIONAL LOGIC

**Transistor Sizing using Logical Effort**

$$F = \frac{C_L}{C_{g1}} = \prod_{1}^{N} \frac{f_i}{b_i} \qquad G = \prod_{1}^{N} g_i \qquad D = t_{p0} \sum_{j=1}^{N} \left( p_j + \frac{f_j g_j}{\gamma} \right)$$

$$B = \prod_{1}^{N} b_i \qquad H = FGB \qquad D_{min} = t_{p0} \left( \sum_{j=1}^{N} p_j + \frac{N(\sqrt[N]{H})}{\gamma} \right)$$