### EECS 312: Digital Integrated Circuits Midterm Exam Solutions

### 13 October 2009

### Robert Dick

Show your work. Derivations are required for credit; end results are insufficient. Closed book. No electronic mental aids.

Signature:

## 1 Qualitative questions

- 1. (10 pts.) Indicate whether each of the following has been increasing  $(\uparrow)$  or decreasing  $(\downarrow)$  with process scaling for synchronous integrated circuits. If you feel the need to qualify your answer, limit the qualification to three words at most.

- (a) Clock frequency:  $\uparrow$

- (b) Power consumption per device per switching event:  $\downarrow$

- (c) Dynamic power consumption as a proportion of total power consumption:  $\downarrow$

- (d)  $t_{ox}$ :  $\downarrow$ , except high-k dielectric

- 2. (10 pts.) Draw the side view of both an NMOSFET and a PMOSFET, showing the locations for source, drain, and gate, and indicating the type(s) of material used in each portion of the structure. Indicate class and concentration of dopants using the standard notation.

| Gate                                |                         | / babe          |           |                                 |

|-------------------------------------|-------------------------|-----------------|-----------|---------------------------------|

| Source SiOz Pohy Si<br>n+Si p Si n+ | or metal<br>Drain<br>Si | Source<br>pt Si | ISION Pol | y Si or netul<br>Drain<br>pt Si |

| NMOSFET                             |                         | PMOSFET         |           |                                 |

- 3. (10 pts.) Using no more than three sentences, each, explain why

- (a) Threshold voltage decreases for very short NMOSFETs and

A portion of the region under the gate is already partially depleted by the source and drain fields. For short transistors, this region is no smaller and therefore has more relative effect.

- (b) Threshold voltage increases for narrow NMOSFETs. In the middle of the transistor, the field effect is similar to that for infinite parallel plates. Near the edges, the fringing effect results in a higher required voltage difference to achieve inversion. For narrow transistors, the appropriate model moves from infinite parallel plates to a line and plate.

- 4. (10 pts.) Use one sentence, each, to answer the following questions:

- (a) Give one reason why the switch from Al to Cu interconnect required moving to the dual Damascene process.

- i. Etching copper to form easily-removed volatile compounds is harder than similarly etching aluminum.

- ii. Copper diffuses into silicon, requiring silicon to be protected by another substance before deposition. Although this is now part of the standard dual Damascene process, and is therefore an acceptable answer, it was not the source of the name of the process.

- (b) Give one reason for an increase in the complexity of individual design rules with process scaling.

As feature sizes reduce relative to exposure light wavelength, the radius of interaction increases in terms of lambda, requiring more rules.

(c) Indicate one important use of CMP during the fabrication process. Planarization between fabrication of metal layers.

## 2 Quantitative questions

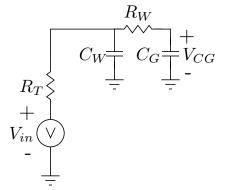

5. (10 pts.) Consider the circuit shown in the following figure.

Given that  $V_{in}$  has been 0 V for a very long time, and changes instantly to 2.5 V at t = 0, derive the expression for  $V_{CG}(t)$ . It is fine to simplify the problem by converting the resistances and capacitances to lump sum values. Please simplify your expression as much as possible. Gross simplifications were accepted for this question. In fact, any answer providing a complete voltage function with approximately the right form, and constants that don't introduce extreme error, was accepted. However, we will soon learn the concept of Elmore delay, after which time a more refined approximation will be possible, and expected. The following answers were accepted.

$$V_{CG}(t) \approx 2.5 \,\mathrm{V}\left(1 - e^{\frac{-t}{\mathrm{anything not crazy}}}\right)$$

The preferred answer is

$$V_{CG}(T) \approx 2.5 \,\mathrm{V}\left(1 - e^{\frac{-t}{R_T C_W + (R_T + R_W)C_G}}\right)$$

Again, note that this answer was not required for full credit on this exam.

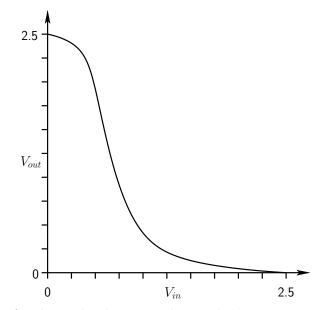

6. (10 pts.) Consider the transfer function shown in the following figure.

Report  $NM_L$  and  $NM_H$  for this technology. I understand that you are estimating these values from the plot so answers within 5% of the right value will be considered correct.

$$NM_L = 0.375 \,\mathrm{V}$$

$NM_H = 1.375 \,\mathrm{V}$

7. (20 pts.) Determine the steady-state current through a floating-output inverter built from minimal-width (i.e., it is an unbalanced inverter) and minimal-length FETs in the default process for each of the following values of  $V_{GS}$ : 0 V and 0.2 V. Show your work.

In both cases, NMOSFET is in the sub-threshold region. The PMOSFET resistance is negligible compared to that of the NMOSFET. We can simplify the problem and derive an approximate solution by assuming that the PMOSFET has no resistance and concentrating on the NMOSFET. More precise solutions were also accepted. Those who wrote the correct expression but did not solve for the numerical values of the exponentials were not penalized.

$$I_D = I_S e^{\frac{V_{GS}}{nkT/q}} \left(1 - e^{\frac{-V_{DS}}{kT/q}}\right)$$

$$I_D(0 V) = 21.0 \text{ pA} e^{\frac{0 V}{1.5 \cdot 25.875 - 3}} \left(1 - e^{\frac{-2.5 V}{25.875 \times 10^{-3}}}\right)$$

$$I_D(0 V) = 21.0 \text{ pA} \left(1 - e^{\frac{-2.5 V}{25.875 \times 10^{-3}}}\right)$$

$$I_D(0 V) = 21 \text{ pA}$$

$$I_D(0.2 V) = 21.0 \text{ pA} e^{\frac{0.2 V}{1.5 \cdot 25.875 \times 10^{-3}}} \left(1 - e^{\frac{-2.5 V}{25.875 \times 10^{-3}}}\right)$$

$$I_D(0.2 V) = 3.63 \text{ nA}$$

A solution using the subthreshold swing expression is also fine.

# 3 Reference material

|      | $C_{OX}$                         | $C_O$                          | $C_j$                            | $m_j$ | $\phi_b$ | $C_{jsw}$                      | $m_{jsw}$ | $\phi_{bsw}$ |

|------|----------------------------------|--------------------------------|----------------------------------|-------|----------|--------------------------------|-----------|--------------|

|      | $(\mathrm{fF}/\mathrm{\mu m^2})$ | $(\mathrm{fF}/\mathrm{\mu m})$ | $(\mathrm{fF}/\mathrm{\mu m^2})$ |       | (V)      | $(\mathrm{fF}/\mathrm{\mu m})$ |           | (V)          |

| NMOS | 6                                | 0.31                           | 2                                | 0.5   | 0.9      | 0.28                           | 0.44      | 0.9          |

| PMOS | 6                                | 0.27                           | 1.9                              | 0.48  | 0.9      | 0.22                           | 0.32      | 0.9          |

## MODELS FOR CMOS DEVICES CMOS (0.25 µm) – Unified Model.

|      | V <sub>70</sub> (V) | γ(V <sup>0.5</sup> ) | $V_{DSAT}(\mathbf{V})$ | k' (A/V <sup>2</sup> ) | $\lambda$ (V <sup>-1</sup> ) |

|------|---------------------|----------------------|------------------------|------------------------|------------------------------|

| NMOS | 0.43                | 0.4                  | 0.63                   | 115 × 10 <sup>-6</sup> | 0.06                         |

| PMOS | -0.4                | -0.4                 | -1                     | -30 × 10 <sup>-6</sup> | -0.1                         |

| CMOS (0.25 µm) - | Switch Model $(R_{eq})$ |

|------------------|-------------------------|

| ··               | - 1                     |

| $V_{DD}(\mathbf{V})$ | 1    | 1.5 | 2  | 2.5 |

|----------------------|------|-----|----|-----|

| NMOS (kΩ)            | · 35 | 19  | 15 | 13  |

| <b>PMOS</b> (kΩ)     | 115  | 55  | 38 | 31  |

### CMOS (0.25 µm) - BSIM Model

See Website: http://bwrc.eecs.berkeley.edu/IcBook

| Name                        | Value                 |

|-----------------------------|-----------------------|

| kT/q                        | $25.875\mathrm{mJ/C}$ |

| NMOSFET $I_S$               | $21.0\mathrm{pA}$     |

| PMOSFET $I_S$               | $41.8\mathrm{pA}$     |

| $n$ (for $I_D$ calculation) | 1.5                   |

# VALUES OF MATERIAL AND PHYSICAL CONSTANTS

| Name                                                                  | Symbol                 | Value                  | Units                       |

|-----------------------------------------------------------------------|------------------------|------------------------|-----------------------------|

| Room temperature                                                      | r                      | 300 (= 27°C)           | к                           |

| Boltzman constant                                                     | k                      | $1.38 \times 10^{-23}$ | J/K                         |

| Electron charge                                                       | q                      | $1.6 \times 10^{-19}$  | С                           |

| Thermal voltage                                                       | $\phi_r = kT/q$        | 26                     | mV (at 300 K)               |

| Intrinsic Carrier<br>Concentration (Silicon)                          | n <sub>i</sub>         | $1.5 \times 10^{10}$   | cm <sup>-3</sup> (at 300 K) |

| Permittivity of Si                                                    | ¢,,                    | $1.05 \times 10^{-12}$ | F/cm                        |

| Permittivity of SiO2                                                  | <b>E</b> <sub>03</sub> | $3.5 \times 10^{-13}$  | F/cm                        |

| Resistivity of Al                                                     | ρ <sub>ΑΙ</sub>        | $2.7 \times 10^{-8}$   | Ω-m                         |

| Resistivity of Cu                                                     | PCu                    | $1.7 \times 10^{-8}$   | <b>Ω-</b> m                 |

| Magnetic permeability<br>of vacuum<br>(similar for SiO <sub>2</sub> ) | μ <sub>0</sub>         | $12.6 \times 10^{-7}$  | Wb/Am                       |

| Speed of light<br>(in vacuum)                                         | <i>c</i> <sub>0</sub>  | 30                     | cm/nsec                     |

| Speed of light (in $SiO_2$ )                                          | C <sub>ex</sub>        | 15                     | cm/nsec                     |

## FORMULAS AND EQUATIONS

### Diode

$$I_{D} = I_{S}(e^{V_{D}/\Phi_{T}} - 1) = Q_{D}/\tau_{T}$$

$$C_{j} = \frac{C_{j0}}{(1 - V_{D}/\phi_{0})^{m}}$$

$$K_{eq} = \frac{-\phi_{0}^{m}}{(V_{high} - V_{low})(1 - m)} \times [(\phi_{0} - V_{high})^{1 - m} - (\phi_{0} - V_{low})^{1 - m}]$$

### **MOS Transistor**

$$V_{T} = V_{T0} + \gamma(\sqrt{|-2\phi_{F} + V_{SB}|} - \sqrt{|-2\phi_{F}|})$$

$$I_{D} = \frac{k'_{n}}{2} \frac{W}{L} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS}) \text{ (sat)}$$

$$I_{D} = \upsilon_{sat} C_{as} W \left( V_{GS} - V_{T} - \frac{V_{DSAT}}{2} \right) (1 + \lambda V_{DS}) \text{ (velocity sat)}$$

$$I_{D} = k'_{n} \frac{W}{L} \left( (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right) \text{ (triode)}$$

$$I_{D} = I_{S} e^{\frac{V_{CS}}{nkT/q}} \left( 1 - e^{-\frac{V_{DS}}{kT/q}} \right) \text{ (subthreshold)}$$

### Deep Submicron MOS Unified Model

$$\begin{split} I_D &= 0 \text{ for } V_{GT} \leq 0 \\ I_D &= k' \frac{W}{L} \left( V_{GT} V_{min} - \frac{V_{min}^2}{2} \right) (1 + \lambda V_{DS}) \text{ for } V_{GT} \geq 0 \\ \text{with } V_{min} &= \min(V_{GT}, V_{DS}, V_{DSAT}) \\ \text{and } V_{GT} &= V_{GS} - V_T \end{split}$$

#### MOS Switch Model

ł

$$\begin{split} R_{rq} &= \frac{1}{2} \bigg( \frac{V_{DD}}{I_{DSAT} (1 + \lambda V_{DD})} + \frac{V_{DD}/2}{I_{DSAT} (1 + \lambda V_{DD}/2)} \bigg) \\ &\approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \bigg( 1 - \frac{5}{6} \lambda V_{DD} \bigg) \end{split}$$

#### Inverter

$$\begin{split} V_{OH} &= f(V_{OL}) \\ V_{OL} &= f(V_{OH}) \\ V_M &= f(V_M) \\ t_p &= 0.69 R_{eq} C_L = \frac{C_L(V_{swing}/2)}{I_{avg}} \\ P_{dyn} &= C_L V_{DD} V_{swing} f \\ P_{stat} &= V_{DD} I_{DD} \end{split}$$

#### Static CMOS Inverter

$$\begin{aligned} &V_{OH} = V_{DD} \\ &V_{OL} = GND \\ &V_{M} \approx \frac{rV_{DD}}{1+r} \quad \text{with} \quad r = \frac{k_p V_{DSATp}}{k_n V_{DSATn}} \\ &V_{IH} = V_M - \frac{V_M}{g} \qquad V_{IL} = V_M + \frac{V_{DD} - V_M}{g} \\ &\text{with} \quad g \approx \frac{1+r}{(V_M - V_{Tn} - V_{DSATn}/2)(\lambda_n - \lambda_p)} \\ &t_p = \frac{t_{pHL} + t_{pLH}}{2} = 0.69 C_L \Big(\frac{R_{eqn} + R_{eqp}}{2}\Big) \\ &P_{av} = C_L V_{DD}^2 f \end{aligned}$$

#### Interconnect

Lumped RC:  $t_p = 0.69 RC$ Distributed RC:  $t_p = 0.38 RC$ RC-chain:

$$\tau_{N} = \sum_{i=1}^{N} R_{i} \sum_{j=i}^{N} C_{j} = \sum_{i=1}^{N} C_{i} \sum_{j=1}^{i} R_{j}$$

Transmission line reflection:

$$\rho \;=\; \frac{V_{refl}}{V_{inc}} \;=\; \frac{I_{refl}}{I_{inc}} \;=\; \frac{R-Z_0}{R+Z_o} \label{eq:rho}$$

# **CMOS COMBINATIONAL LOGIC**

**Transistor Sizing using Logical Effort**

$$F = \frac{C_L}{C_{g_1}} = \prod_{i=1}^{N} \frac{f_i}{b_i} \qquad G = \prod_{i=1}^{N} g_i \qquad D = t_{p0} \sum_{j=1}^{N} \left( p_j + \frac{f_j g_j}{\gamma} \right)$$

$$B = \prod_{i=1}^{N} b_i \qquad H = FGB \qquad D_{min} = t_{p0} \left( \sum_{j=1}^{N} p_j + \frac{N(\sqrt[N]{H})}{\gamma} \right)$$