# Embedded Systems: An Application-Centered Approach

#### Robert Dick

http://robertdick.org/esaca/ Office: 2417-E EECS Department of Electrical Engineering and Computer Science University of Michigan

Two major sources of changing problems

New implementation technologies.

New applications.

## Outline

- 1. Evolution of computation

- 2. Carbon nanotubes

- 3. Single-electron tunneling transistors

### Evolution of computation

- 1800s: Mechanical

- Late 1800s-early 1900s: Electro-mechanical

- Early 1900s-mid 1900s: Vacuum tube electronic

- Mid 1900s-late 1900s: Bipolar (TTL)

- Late 1900s-early 2000s: MOS

Evolution of computation

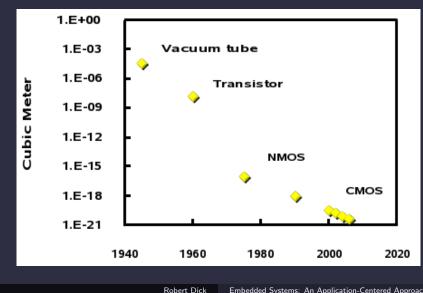

### Impact of scaling on volume

Evolution of computation

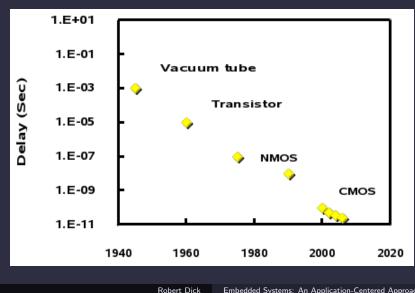

### Impact of scaling on delay

Evolution of computation

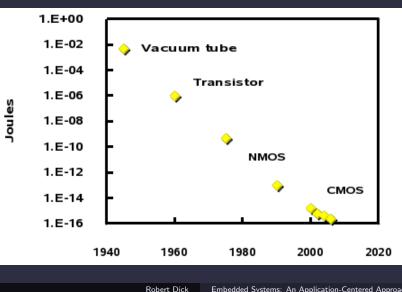

### Impact of scaling on energy consumption

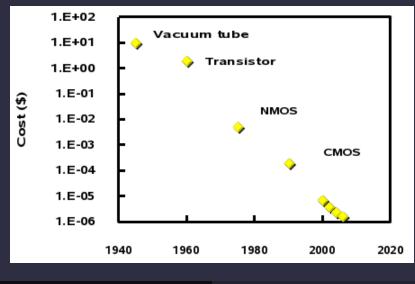

### Impact of scaling on price

## Scaling trends

| High Volume<br>Manufacturing | 2004             | 2006 | 2008 | 2010                          | 2012 | 2014 | 2016 | 2018 |

|------------------------------|------------------|------|------|-------------------------------|------|------|------|------|

| Technology Node<br>(nm)      | 90               | 65   | 45   | 32                            | 22   | 16   | 11   | 8    |

| Integration<br>Capacity (BT) | 2                | 4    | 8    | 16                            | 32   | 64   | 128  | 256  |

| Delay = CV/l<br>scaling      | 0.7              | ~0.7 | >0.7 | Delay scaling will slow down  |      |      |      |      |

| Energy/Logic Op<br>scaling   | >0.35            | >0.5 | >0.5 | Energy scaling will slow down |      |      |      |      |

| Bulk Planar CMOS             | High Probability |      |      | Low Probability               |      |      |      |      |

| Alternate, 3D etc            | Low Probability  |      |      | High Probability              |      |      |      |      |

| Variability                  | Medium           |      |      | High Very High                |      |      |      |      |

| Inter-Ir dielectric k        | ~3 <3            |      |      | Reduce slowly towards 2-2.5   |      |      |      |      |

| RC Delay                     | 1                | 1    | 1    | 1                             | 1    | 1    | 1    | 1    |

| Metal Layers                 | 6-7              | 7-8  | 8-9  | 0.5 to 1 layer per generation |      |      |      |      |

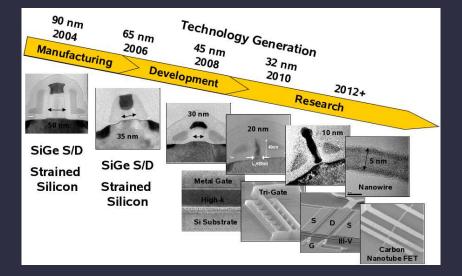

### Device trends

Robert Dick Embedded Systems: An Application-Centered Approach

Advantages of CMOS relative to prior technologies

- Performance

- Gain, low noise

- Area

- Massive integration

- Power

- Reliability

- Fabrication difficulty & cost

## Current status for CMOS

- 32 nm

- Power, thermal problems severe

- Fabrication cost per design high

- Potential reliability problems in future

- Soft errors

- Electromigration, dielectric breakdown, etc.

- Process variation

- Soon: Discrete dopant problems

## Computing trends applications

- Increased market volume and size for portable and embedded systems compared to general-purpose computers.

- Instructor's opinion: Embedded will grow in importance in the future.

- High-performance general-purpose computing will still matter.

- Much of the general-purpose computation will move to data centers.

Advantages of alternative nanotechnologies

May allow continued process scaling after CMOS scaling impractical.

- Candidates

- Carbon nanotube

- Nanowire Single electron tunneling transistors

### Comparison of nanoscale technologies

|                                                  | Table 5       | 9 Emergi     | ng Research L                                                                              | ogic Devices–                 | Demonstrated                                                      | Projected Par                                              | ameters                                |                                           |

|--------------------------------------------------|---------------|--------------|--------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------|-------------------------------------------|

| Device                                           |               | ł            | -                                                                                          |                               |                                                                   | ¢                                                          | $\square$                              |                                           |

|                                                  |               | FET [B]      | 1D structures                                                                              | Resonant<br>Tunneling Devices | SET                                                               | Molecular                                                  | Ferromagnetic<br>logic                 | Spin transistor                           |

| Ţ                                                | vpes          | Si CMOS      | CNT FET<br>NW FET<br>NW hetero-<br>structures<br>Crossbar<br>nanostructure                 | RTD-FET<br>RTT                | SET                                                               | Crossbar latch<br>Molecular<br>transistor<br>Molecular QCA | Moving domain<br>wall<br>M: QCA        | Spin transistor                           |

| Supported                                        | Architectures | Conventional | Conventional<br>and Cross-bar                                                              | Conventional<br>and CNN       | CNN                                                               | Cross-bar and<br>QCA                                       | CNN<br>Reconfigure<br>logic and<br>QCA | Conventional                              |

| Cell Size                                        | Projected     | 100 nm       | 100 nm [C]                                                                                 | 100 nm [C]                    | 40 nm [L]                                                         | 10 nm [Q]                                                  | 140 nm [U]                             | 100 nm [C]                                |

| (spatial pitch)                                  | Demonstrated  | 590 nm       | ~1.5 µm [D]                                                                                | 3µm [H]                       | ~700 nm [M]                                                       | ~2µm [R]                                                   | 250 nm [V, W]                          | 100 µm [X]                                |

| Density<br>(device/cm <sup>2</sup> )             | Projected     | 1E10         | 4.5E9                                                                                      | 4.5E9                         | 6E10                                                              | 1E12                                                       | 5E9                                    | 4.5E9                                     |

|                                                  | Demonstrated  | 2.8E8        | 4E7                                                                                        | 1E7                           | 2E8                                                               | 2E7                                                        | 1.6E9                                  | 1E4                                       |

| 0                                                | Projected     | 12 THz       | 6.3 THz [E]                                                                                | 16 THz [I]                    | 10 THz [M]                                                        | 1 THz [S]                                                  | 1 GHz [U]                              | 40 GHz [Y]                                |

| Switch Speed                                     | Demonstrated  | 1 THz        | 200 MHz [F]                                                                                | 700 GHz [J]                   | 2 THz [N]                                                         | 100 Hz [R]                                                 | 30 Hz [V, W]                           | Not known                                 |

| C                                                | Projected     | 61 GHz       | 61 GHz [C]                                                                                 | 61 GHz [C]                    | 1 GHz [L]                                                         | 1 GHz [Q]                                                  | 10 MHz [U]                             | Not known                                 |

| Circuit Speed                                    | Demonstrated  | 5.6 GHz      | 220 Hz [G]                                                                                 | 10 GHz [Z]                    | 1 MHz [F]                                                         | 100 Hz [R]                                                 | 30 Hz [V]                              | Not known                                 |

| Switching<br>Energy, J                           | Projected     | 3E-18        | 3E-18                                                                                      | >3E-18                        | 1×10 <sup>-18</sup> [L]<br>[>1.5×10 <sup>-17</sup> ] [O] 5E-17 [T |                                                            | ~1E-17 [V]                             | 3E-18                                     |

|                                                  | Demonstrated  | 1E-16        | 1E-11 [G]                                                                                  | 1E-13 [K]                     | 8×10 <sup>-17</sup> [P]<br>[>1.3×10 <sup>-14</sup> ] [O]          | 3E-7 [R]                                                   | 6E-18 [W]                              | Not known                                 |

| Binary<br>Throughput,<br>GBit/ns/cm <sup>2</sup> | Projected     | 238          | 238 [C]                                                                                    | 238 [C]                       | 10                                                                | 1000                                                       | 5E-2                                   | Not known                                 |

|                                                  | Demonstrated  | 1.6          | 1E-8                                                                                       | 0.1                           | 2E-4                                                              | 2E-9                                                       | 5E-8                                   | Not known                                 |

| Operationa                                       | l Temperature | RT           | RT                                                                                         | 4.2 - 300 K                   | 20 K [L]                                                          | BT                                                         | RT                                     | RT                                        |

| Materia                                          | als System    | SI           | CNT,<br>Si, Ge, III-V,<br>In <sub>2</sub> O <sub>3</sub> , ZnO,<br>TiO <sub>2</sub> , SiC, | III-V<br>Si-Ge                | III-V<br>Si                                                       | Organic<br>molecules                                       | Ferromagnetic<br>alloys                | Si, III-V,<br>complex<br>metals<br>oxides |

| Research activ                                   | rity [A]      |              | 171                                                                                        | 88                            | 65                                                                | 204                                                        | 25                                     | 102                                       |

#### Credit to ITRS'05 report on Emerging Research Devices.

Robert Dick

## Outline

- 1. Evolution of computation

- 2. Carbon nanotubes

- 3. Single-electron tunneling transistors

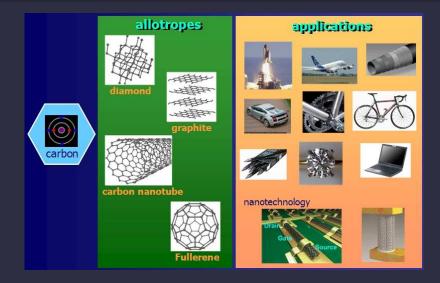

### Carbon

Robert Dick

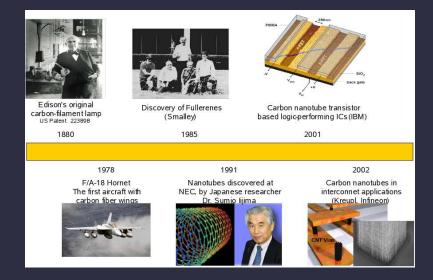

## **CNT** history

Embedded Systems: An Application-Centered Approach

Robert Dick

18

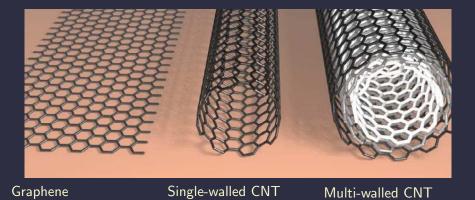

### **CNT** classes

## Chirality

Embedded Systems: An Application-Centered Approach

Robert Dick

## Metallic and semiconducting CNTs

#### Armchair (metallic)

#### Zigzag (semi-conducting)

## **CNT** properties

- Metallic or semiconducting.

- Diameter: 0.4–100 nm.

- Length: up to millimeters.

- Ballistic transport.

- Excellent thermal conductivity.

- Very high current density.

- High chemical stability.

- Robust to environment.

- Tensile strength: 45 TPa.

- Steel is 2 TPa.

- Temperature stability

- 2,800°C in vacuum.

- 700°C in air.

### CNTs compared with Cu

| Property               | CNT                                   | Cu             |

|------------------------|---------------------------------------|----------------|

| Max I dens. $(A/cm^2)$ | $> 1 	imes 10^9$ (Wei et al., APL'01) | $1 	imes 10^7$ |

| Thermal cond. (W/mK)   | 5,800 (Hone et al., Phy Rev B'99)     | 385            |

| Mean free path (nm)    | > 1,000 (McEuen et al. T Nano'02)     | 40             |

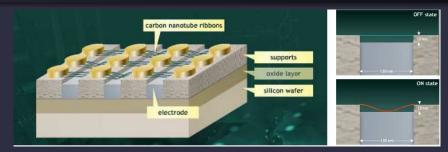

## NRAM

- Uses Van der Waals forces.

- Non-volatile.

- SRAM-like speed.

- DRAM-like density.

- Ready for market in 2007 (and 2008, and 2009, and 2010, and 2011).

- IEEE Spectrum loser of the year. Why?

## Outline

- 1. Evolution of computation

- 2. Carbon nanotubes

- 3. Single-electron tunneling transistors

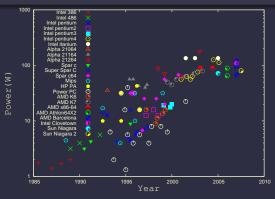

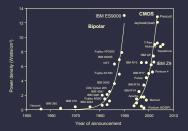

### Power challenges

High-performance applications: energy cost, temperature, reliability Portable embedded systems: battery lifetime

What does history teach us about power consumption?

Device innovations have been the most effective method

- Vacuum tube to semiconductor device in the 1960s

- Bipolar device to CMOS transistor in the 1990s

Based on diagram by C. Johnson, IBM Server and Technology Group

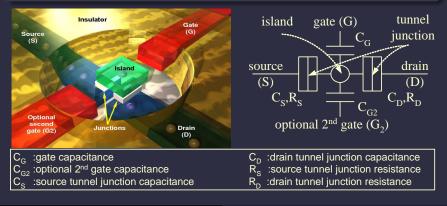

## Single electron tunneling transistor structure

#### Device structure

- Island, terminals (source, drain, gate)

- Electron tunneling through tunneling junctions

Robert Dick

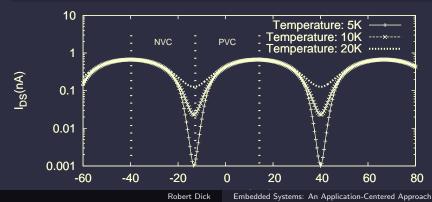

## Single electron tunneling transistor behavior

#### Physical principles

- Coulomb charging effect governs electron tunneling

- Coulomb blockade  $V_{GS} = me/C_G$ ,  $m = \pm 1/2, \pm 3/2, \cdots$  OFF,  $m = 0, \pm 1, \pm 2, \cdots$  ON

## SET properties and challenges

Ultra low power

• Projected energy per switching event  $(1 imes 10^{-18} ext{ J})$

#### Room temperature and fabrication challenge

Electrostatic charging energy must be greater than thermal energy

•

$$e^2/C_{\Sigma} > k_B T$$

• Requires  $e^2/C_{\sum} > 10 k_B T$  or even  $e^2/C_{\sum} > 40 k_B T$

## SET properties and challenges

#### Performance challenge

- Electrons must be confined in the island

- $R_{S}, R_{D} > h/e^{2}, \ h/e^{2} = 25.8 \, \mathrm{k}\Omega$

- High resistance, low driving strength

#### Reliability concerns

- Tunneling between charge traps cause run-time errors

- Unknown before fabrication

- Device technology: Improved by silicon islands

- Reliable design: Post-fabrication adaptation

- Run-time error correction

# Summary

- CMOS will be mainstream for years to come, but not forever.

- The meaning of integrated circuits will change in the future.

- Circuit and logic design fundamentals will still apply.

- Some rules, e.g., difficulty of implementing non linearly separable functions, may change.

- You will each need to adapt as the rules governing device behavior change, but this will be much faster now that you have a foundation.