Power Deregulation: Eliminatring Off-Chip Voltage Regulation Circuitry from Embedded Systems

Seunghoon Kim

Robert P. Dick, Russ Joseph

Mobile Handset R&D Center LG Electronics Seoul, Korea 153-801 romuald@lge.com (research primarily at Northwestern) EECS Department Northwestern University Evanston, IL 60208, U.S.A. dickrp@northwestern.edu rioseph@ece.northwestern.edu

## Motivation

## Costs of regulation

- Up to 30% of overall PCB area

- · Costs, weight, form factor

- Energy conversion inefficiency

- Instability

### Kim, Dick, and Joseph Power Deregulat

#### Technique Experiments

Power deregulation built upon the following technologies

#### Dynamic Frequency Scaling

- · Operating frequency adapt to changing battery voltage

- · Frequency determined by function of  $V_{DD}$

- Power gating

#### Chip-level multiprocessors

- · Already commonly used in general-purpose and embedded computing applications

- $\cdot\,$  Many multimedia applications exhibit high level of parallelism

- $\cdot\,$  Greater parallelism means more performance gained from power deregulation technique

- $\cdot\,$  Power deregulation is designed for embedded systems equipped with multi-core processors

#### Kim, Dick, and Joseph Power Dere

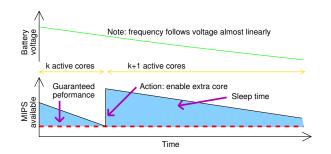

## Power deregulation over time

Power Deregulation

### Quick look at the procedure

$\cdot\,$  Begin with a single core of the chip multi-processor.

Kim Dick and Joseph Po

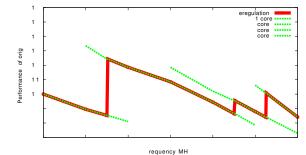

- $\cdot\,$  Processor performance diminishes as battery supplied voltage level drops

- · Compensate by turning on remaining cores if the system does not meet the required performance level

## Benefits of power deregulation

### For manufacturing

- Smaller compact form

- · Integrate more features and design flexibility

- · Cost saving

#### Reliability gains

- $\cdot\,$  Possibility of circuit breakdown from long time scale degradation

- $\cdot\,$  Unstable processor voltage due to I-R switching activity

Kim, Dick, and Joseph Power Deregulat

## Related Works

Many including Telos sensor node have shown that embedded systems can operate directly from raw battery outputs without voltage regulation

#### Means of minimizing power dissipation

- Telos approach applies low operating voltage to a single-core processor (underclocking), which means low performance

- Power deregulation maintaining minimal performance level and preventing leakage power (both static and dynamic) by utilizing sleep mode

Dick and Joseph

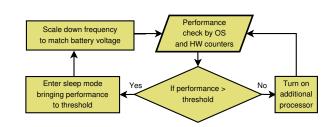

## Power deregulation procedure

Kim, Dick, and Joseph Power

#### Performance requirement

$\cdot~$  85% performance boundary set for calculation purpose

Technique

$\cdot$  Performance level maintained at its minimum

#### Sleep mode

- $\,\cdot\,$  At performance level greater than 85%, task can be done early

- $\cdot\,$  Sleep mode used to conserve power for remaining time

- $\cdot\,$  Even static power can be conserved

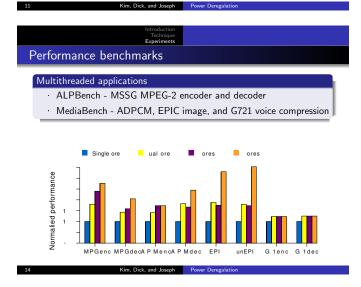

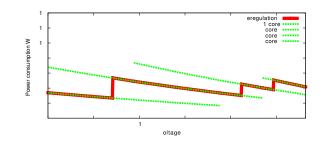

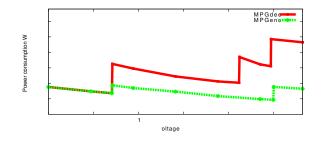

Technique Experiments Power dissipation for MPEG-2 decoder

· Variation of power consumption during lifetime of the battery

Kim, Dick, and Joseph Power Dere

Findings

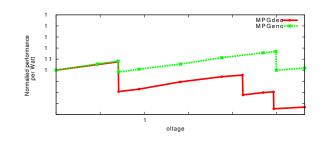

| Deregulated system has similar transition patterns for both performance and power metrics        |   |

|--------------------------------------------------------------------------------------------------|---|

| Transition points depend on parallelism efficiency for different benchmarks                      | 7 |

| Higher parallelism application comprises, transition points are observed at lower voltage points |   |

| Thus, showing higher performance per Watt                                                        |   |

Kim, Dick, and Joseph

### Experimental setup

#### Simulation environment

- M5 multiprocessor simulator

- · DEC Alpha 21164 (EV5) model simulation

- $\cdot\,$  Basic instruction set architecture similar to RISC architectures

- $\cdot\,$  Reconfigured to pipelined in-order processor to better represent embedded systems

#### Power modeling

$\cdot\,$  Baseline architecture: nominal  $V_{DD}$  of 3.3 V at 500 MHz

Kim, Dick, and Joseph Power Dereg

- $\cdot$  Computation of both dynamic and static power

- $\cdot$  Sleep mode consideration applied

## Relative performance for MPEG-2 decoder

requeitcy with

Dick, and Joseph Power D

## Power dissipation with sleep mode power saving

Technique Technique Experiments Relative performance per Watt

For MPGenc, Performance per Watt increases as voltage decreases and number of processor increases

Kim, Dick, and Jos

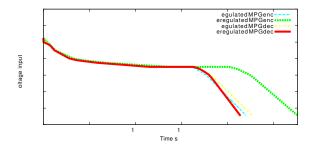

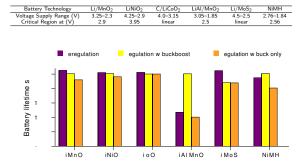

### Battery discharge curve on Li/MnO<sub>2</sub> battery

Technique Experiments

## Battery lifespan comparison with regulated setups

# Battery lifespan - buck-boost effect

Kim Dick and los

#### Buck-Boost and Buck-only Effect

- · Conversion efficiency of 85% assumed for regulation

- · Buck converter for voltage regulation

- $\cdot\,$  Buck-Boost allows battery utilization at a voltage beyond minimum level demanded by CPU

- Full use of battery energy is assumed for buck-boost model

- · Deregulated system performs best in almost all cases

#### Technique Experiments

Kim, Dick, and Joseph Power Deregulat

#### Voltage level at plateau in discharge curve

- · Significant factor in determinant comparable battery life

- · Optimal if the highest point of performance per Watt is observed at this level

Acknowledgments

Collaborators

Prof. David Brooks – Harvard University

#### Support

- · NSF CNS-0720820 (Program officer: Dr. Helen Gill)

- · NSF CNS-0347941 (Program officer: Dr. Helen Gill)

Kim, Dick, and Joseph Power Deregu

Higher parallelism efficiency leads to greater potential battery lifetime as number of processors increase

Kim, Dick, and Joseph Power Deregu

Kim, Dick, and Joseph Power Deregulati

```

Summary

```

#### Power Deregulation

Additional core activation to compensate for diminished performance from reducing battery voltage

- · PCB area reduction by 30%

- · Elimination of regulatory components

- · Comparable battery life span to regulation systems

Kim, Dick, and Joseph Power Dereg

Sufficiently high parallelism efficiency is required