ierische Mathemate

70l. 5, No. 6, p. 345, 199 . 9 No. 1, pp. 11-12, 199 iterpreted Elements, 201 ia, January 1997, 1901 for Hardware/Software, June 2003, 2005, 2005, 2005 78

# Embedded Computing Systems and Hardware/Software Co-Design

yne Wolf

University

#### CONTENTS

|      | Introduction                                             | 78-1  |

|------|----------------------------------------------------------|-------|

| 78.1 | Introduction                                             | 78-1  |

| 78.2 | Uses of Microprocessors<br>Embedded System Architectures |       |

| 78.3 | Embedded System Architectures                            | 78-6  |

| 78.4 | Hardware/Software Co-Design                              | 78-7  |

|      | 78.4.1 Models                                            | 78-7  |

|      | 78.4.2 Co-Simulation                                     | 78-7  |

|      | 78.4.4 Hardware/Software Co-Synthesis                    | 78-9  |

|      | 78.4.5 Design Methodologies                              | 78-10 |

# 18.1 Introduction

This chapter describes embedded computing systems that make use of microprocessors to implement part of the system's function. It also describes hardware/software co-design, which is the process of designing embedded systems while simultaneously considering the design of its hardware and software dements.

# 78.2 Uses of Microprocessors

In embedded computing system (or more simply an embedded system) is any system which uses a mogrammable processor but itself is not a general purpose computer. Thus, a personal computer is not an embedded computing system (though PCs are often used as platforms for building embedded systems), but a telephone or automobile which includes a CPU is an embedded system. Embedded systems may offer some amount of user programmability—3Com's PalmPilot, for example, allows users to write and download tograms even though it is not a general-purpose computer—but embedded systems generally run limited sts of programs. The fact that we know the software that we will run on the hardware allows us to optimize both the software and hardware in ways that are not possible in general-purpose computing systems.

Microprocessors are generally categorized by their word size, since word size is associated both with with program size and data resolution. Commercial microprocessors come in many sizes; the term is used to denote a microprocessor which comes with some basic on-chip peripheral

78-2 The VLSI Ha

devices, such as serial input/output (I/O) ports. Four-bit microcontrollers are extremely since capable of some basic functions. Eight-bit microcontrollers are workhorse low-end microprosisteen- and 32-bit microprocessors provide significantly more functionality. A 16/32-bit micropromay be in the same architectural family as the CPUs used in computer workstations, but microprodestined for embedded computing often do not provide memory management hardware. A digital processor (DSP) is a microprocessor tuned for signal processing applications. DSPs are often architectures, meaning that they provide separate data and program memories; Harvard architectures, in the provide higher performance for DSP applications. DSPs may provide integer or floating-point ariteration.

Microprocessors are used in an incredible variety of products. Furthermore, many products consultiple microprocessors. Four- and eight-bit microprocessors are often used in appliances: for example a thermostat may use a microcontroller to provide timed control of room temperature. Automaterial automaterial cameras often use several eight-bit microprocessors, each responsible for a different aspect of camera's functionality: exposure, shutter control, etc. High-end microprocessors are used in laser a ink-jet printers to control the rendering of the page. Many printers use two or three microprocessor to handle generation of pixels, control of the print engine, and so forth. Modern automobiles may close to 100 microprocessors, and even inexpensive automobiles generally contain several. High-emicroprocessors are used to control the engine's ignition system—automobiles use sophisticated contains algorithms to simultaneously achieve low emissions, high fuel economy, and good performance. In end microcontrollers are used in a number of places in the automobile to increase functionality; example, four-bit microcontrollers are often used to sense whether seat belts are fastened and turn the seat belt light when necessary.

Microprocessors may replace analog components to provide similar functions, or they may add total new functionality to a system. They are used in several different ways in embedded systems. One broad application category is signal conditioning, in which the microprocessor or DSP performs some filtered or control function on a digitized input. The conditioned signal may be sent to some other microprocessor for final use. Signal conditioning allows systems to use less-expensive sensors with the application of relatively inexpensive microprocessor. Beyond signal conditioning, microprocessors may be used for more sophisticated control applications. For example, microprocessors are often used in telephone systems to control signaling functions, such as determining what action to take based on the reception of dial tones etc. Microprocessors may implement user interfaces; this requires sensing when buttons, knobs, etc. are used, taking appropriate actions, and updating displays. Finally, microprocessors may perform data processing, such as managing the calendar in a personal digital assistant.

There are several reasons why microprocessors make good design components in such a wide variety application areas. First, digital systems often provide more complex functionality than can be created using analog components. A good example is the user interface of a home audio/video system, which provide more information and is easier use than older, non-microprocessor-controlled systems. Microprocessor

also allow related products much more cost-effectively. An entire product family, including models a various price and feature points, can be built around a single microprocessor-based platform. The platform includes both hardware components common to all the family members and software running on the microprocessor to provide functionality. Software elements can easily be turned on or off in various family members. Economies of scale often mean that it is cheaper to put the same hardware in both expensive and cheap models and to turn off features in the inexpensive models rather than to try to optimize the hardware and software configurations of each model separately. Microprocessors also allow design changes to be made much more quickly. Many changes may be possible simply by reprogramming; other features may be made possible by adding memory or other simple hardware changes along with some additional programming. Finally, microprocessors aid in concurrent engineering. After some initial design decisions have been made, hardware and software can be designed in parallel, reducing total design time.

While embedded computing systems traditionally have been fabricated at the board level out multiple chips, embedded computing systems will play an increasing role in integrated circuit desawell. As VLSI technology moves toward the ability to fabricate chips with billions of transitories.

llers are extremely simp orse low-end microproce lity. A 16/32-bit microproc rkstations, but microproce ment hardware. A digital ations. DSPs are often Har emories; Harvard architecture ger or floating-point arithmen rmore, many products conta used in appliances: for example room temperature. Automat e for a different aspect of rocessors are used in laser and e two or three microprocessor . Modern automobiles may us ally contain several. High-er obiles use sophisticated contra , and good performance. Low le to increase functionality: fo belts are fastened and turn or

nctions, or they may add totally embedded systems. One broad or DSP performs some filtering nt to some other microprocessor ensors with the application of a processors may be used for more en used in telephone systems to d on the reception of dial tones ng when buttons, knobs, etc. are oprocessors may perform data

conents in such a wide variety of onality than can be created using lio/video systems, which provide trolled systems. Microprocesson uct family, including models a sor-based platform. The platforms and software running on the urned on or off in various family hardware in both expensive and a to try to optimize the hardware reprogramming; other featurenges along with some additional feer some initial design decisions cing total design time.

cated at the board level out of role in integrated circuit designings with billions of transisters ated circuits will increasingly incorporate one or several microprocessors executing embedded re. Using microprocessors as components in integrated circuits increases design productivity, CPUs can be used as large components which implement a significant part of the system function-single-chip embedded systems can provide much higher performance than board-level equivalents, thip-to-chip delays are eliminated.

# **Embedded System Architectures**

ough embedded computing spans a wide range of application areas, from automotive to medical, are some common principles of design for embedded systems. The application-specific embedded are runs on a hardware platform. An example hardware platform is shown in Figure 78.1. It contains croprocessor, memory, and I/O devices. When designing on a general-purpose system such as a PC, ardware platform would be predetermined, but in hardware/software co-design the software and ware can be designed together to better meet cost and performance requirements.

pending on the application, various combinations of criteria may be important goals for the system n. Two typical criteria are speed and manufacturing cost. The speed at which computations are made contributes to the general usability of the system, just as in general-purpose computing. However, mance is also often associated with the satisfaction of deadlines—times at which computations be completed to ensure the proper operation of the system. If failure to meet a deadline causes a or error, it is termed a hard deadline. And missed deadlines, which result in tolerable but unsatisfactory adations are called soft deadlines. Hard deadlines are often (though not always) associated with safetycal systems. Designing for deadlines is one of the most challenging tasks in embedded system design. ufacturing cost is often an important criteria for embedded systems. Although the hardware coments ultimately determine manufacturing cost, software plays an important role as well. First, the size e program determines the amount of memory required, and memory is often a significant component he total component cost. Furthermore, the improper design of software can cause one to require er-performance, more-expensive hardware components than are really necessary. Efficient utilization ardware resources requires careful software design. Power consumption is becoming an increasingly ortant design metric. Power is certainly important in battery-operated devices, but it can be important all socket-powered systems as well—lower power consumption means smaller, less-expensive power plies and cooling and may result in environmental ratings that are advantageous in the marketplace. e again, power consumption is ultimately determined by the hardware, but software plays a significant in power characteristics. For example, more efficient use of on-chip caches can reduce the need for thip memory access, which consumes much more power than on-chip cache references.

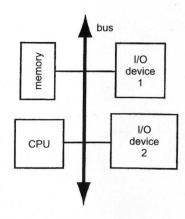

FIGURE 78.1 Hardware structure of a microprocessor system.

Figure 78.1 shows the hardware architecture of a basic microprocessor system. The system the CPU, memory, and some I/O devices, all connected by a bus. This system may consist of chips for high-end microprocessors or a single-chip microcontroller. Typical I/O devices analog/digital (ADC) and digital/analog (DAC) converters, serial and parallel communication network and bus interfaces, buttons and switches, and various types of display devices. This cration is a complete, basic, embedded computing hardware platform on which application can execute.

The embedded application software includes components for managing I/O devices and for perform the core computational tasks. The basic software techniques for communicating with I/O device polling and interrupt-driven. In a polled system, the program checks each device's status registed determine if it is ready to perform I/O. Polling allows the CPU to determine the order in which operations are completed, which may be important for ensuring that certain device requests are satisfated the proper rate. However, polling also means that a device may not be serviced in time if the program does not check it frequently enough. Interrupt-driven I/O allows a device to change the forcontrol on the CPU and call a device driver to handle the pending I/O operation. An interrupt may provide both prioritized interrupts to allow some devices to take precedence over others and vector interrupts to allow devices to specify which driver should handle their request.

Device drivers, whether polled or interrupt-driven, will typically perform basic device-specific futions and hand-off data to the core routines for processing. Those routines may perform relatively sint tasks, such as transducing data from one device to another, or may perform more sophisticated algorith such as control. Those core routines often will initiate output operations based on their computation the input operations.

Input and output may occur either periodically or aperiodically. Sampled data is a common example of periodic I/O, while user interfaces provide a common source of aperiodic I/O events. The nature of the I/O transactions affects both the device drivers and the core computational code. Code which operation periodic data is generally driven by a timer which initiates the code at the start of the period. Periodic operations are often characterized by their periods and the deadline for each period. Aperiodic I/O make the detected either by an interrupt or by polling the devices. Aperiodic operations may have deadline which are generally measured from the initiating I/O event. Periodic operations can often be thought as being executed within an infinite loop. Aperiodic operations tend to use more event-driven code, which various sections of the program are exercised by different aperiodic events, since there is often more than one aperiodic event which can occur.

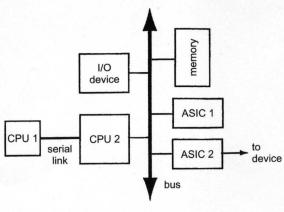

Embedded computing systems exhibit a great deal of parallelism which can be used to speed a computation. As a result, they often use multiple microprocessors which communicate with each other to perform the required function. In addition to microprocessors, application-specific ICs (ASICs) must be added to accelerate certain critical functions. CPUs and ASICs in general are called processing element (PEs). An example multiprocessor system built from several PEs along with I/O devices and memory is shown in Figure 78.2.

The choice of several small microprocessors or ASICs rather than one large CPU is primarily determined by cost. Microprocessor cost is a nonlinear function of performance, even within a microprocessor family. Vendors generally supply several versions of a microprocessor which run at different clock rates chips which run at varying speeds are a natural consequence of the variations in the VLSI manufacturary process. The slowest microprocessors are significantly less expensive than the fastest ones, and the cost increment is larger at the high end of the speed range than at the low end. As a result, it is often cheaper to use several smaller microprocessors to implement a function.

When several microprocessors work together in a system, they may communicate with each other is several different ways. If slow data rates are sufficient, serial data links are commonly used for their is hardware cost. The I<sup>2</sup>C bus is a well-known example of a serial bus used to build multi-microprocess embedded systems; the CAN bus is widely used in automobiles. High-speed serial links can achieve moderately high performance and are often used to link multiple DSPs in high-speed signal processor.

Parallel d uch as PC oftware to eral-purpo x enough t em into p ng system the proc inction is t s core algo ed is a func I-time oper e are a nu: to determ: form to det can obviou ot be able to ready. n general, n scheduli al-purpose -priority r in fair acc eting deac ındamenta des a set o he deadline s of the pr e are no ling polic and do n

rter the I

eir deadl

ling polic

re not kn

n. The system nay consist of al I/O devices immunication devices. This control

ices and for performing with I/O devices rice's status register he order in which he order in which he requests are satisfied in time if the CP e to change the flow 1. An interrupt system of the control of the contro

c device-specific fun rform relatively simp phisticated algorithm on their computation

is a common example events. The nature of Code which operates of the period. Periodic John Aperiodic I/O may a may have deadlines in often be thought of event-driven code, in s, since there is often

be used to speed up ticate with each other cific ICs (ASICs) may d processing elements evices and memory is

U is primarily deterhin a microprocessor different clock rates VLSI manufacturing st ones, and the cost llt, it is often cheaper

te with each other in ily used for their low nulti-microprocessor al links can achieve eed signal processing

FIGURE 78.2 A heterogeneous embedded multiprocessor.

s. Parallel data links provide the highest performance thanks to their sheer data width. High-speed such as PCI can be used to link several processors.

e software for an embedded multiprocessing system is often built around processes. A process, as general-purpose computing system, is an instantiation of a program with its own state. Since problems plex enough to require multiprocessors often run sophisticated algorithms and I/O systems, dividing ystem into processes helps manage design complexity. A real-time operating system (RTOS) is an ating system specifically designed for embedded, and specifically real-time applications. The RTOS ages the processes and device drivers in the system, determining when each executes on the CPU. function is termed scheduling. The partitioning of the software between application code which utes core algorithms and an RTOS which schedules the times to which those core algorithms are uted is a fundamental design principle in computing systems in general and is especially important eal-time operation.

there are a number of techniques which can be used to schedule processes in an embedded system—

is, to determine which process runs next on a particular CPU. Most RTOSs use process priorities in

me form to determine the schedule. A process may be in any one of three states: currently executing

here can obviously be only one executing process on each CPU); ready to execute; or waiting. A process

of not be able to execute until, for example, its data has arrived. Once its data arrives, it moves from

the scheduler chooses among the ready processes to determine which process runs

on. In general, the RTOS's scheduler chooses the highest-priority ready process to run next; variations

tween scheduling methods depend in large part on the ways in which priorities are determined. Unlike

metal-purpose operating systems, RTOSs generally allow a process to run until it is preempted by a

ther-priority process. General-purpose operating systems often perform time-slicing operations to

matain fair access of all the users on the system, but time-slicing does not allow the control required

meeting deadlines.

A fundamental result in real-time scheduling is known as rate-monotonic scheduling. This technique dedules a set of processes which run independently on a single CPU. Each process has its own period, the deadline happening at the end of each period. There can be arbitrary relationships between the processes. It is assumed that data does not in general arrive at the beginning of the period, there are no assumptions about when a process goes from waiting to ready within a period. This deduling policy uses static priorities—the priorities for the processes are assigned before execution and do not change. It can be shown that the optimal priority assignment is based on period—shorter the period, the higher the priority. This priority assignment ensures that all processes will be their deadlines on every period. It can also be shown that at most, 69% of the CPU is used by this deduling policy. The remaining cycles are spent waiting for activities to happen—since data arrival are not known, it is not possible to utilize 100% of the CPU cycles.

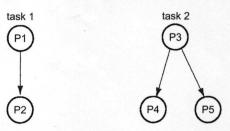

FIGURE 78.3 A task graph with two tasks and data dependencies between processes,

Another well-known, real-time scheduling technique is earliest deadline first (EDF). This is a depriority scheme—process priorities change during execution. EDF sets priorities based on the impriority scheme deadlines, with the process whose deadline is closest in the future having the highest priority. the rate of change of process priorities depends on the periods and deadlines. EDF can be shown be able to utilize 100% of the CPU, but it does not guarantee that all deadlines will be met. Sie priorities are dynamic, it is not possible in general to analyze whether the system will be overloss at some point.

Processes may be specified with data dependencies, as shown in Figure 78.3, to create a task en An arc in the data dependency graph specifies that one process feeds data to another. The sink process cannot become ready until all the source processes have delivered their data. Processes which have data dependency path between them are in separate tasks. Each task can run at its own rate. Date dependencies allow schedulers to make more efficient use of CPU resources. Since the source and so processes of a data dependency cannot execute simultaneously, we can use that information to eliminate to the control of the c some combinations of processes which may want to run at the same time. Narrowing the scope of processes conflicts allows us to more accurately predict how the CPU will be used.

A real-time operating system is often designed to have a small memory footprint, since embedded systems are more cost-sensitive than general-purpose computers. RTOSs are also designed to be more responsive in two different ways. First, they allow greater control over the order of execution of processes. which is critical for ensuring that deadlines are met. Second, they are designed to have lower contentswitching overhead, since that overhead eats into the time available for meeting deadlines. The kern of an RTOS is the basic set of functions that is always resident in memory. A basic RTOS may have an extremely small kernel of only a few hundred instructions. Such microkernels often provide only basic context-switching and scheduling facilities. More complex RTOSs may provide high-end operating system functions such as file systems and network support; many high-end RTOSs are POSIX (a Unit standard) compliant. While running such a high-end operating system requires more hardware resource the extra features are useful in a number of situations. For example, a controller for a machine on manufacturing line may use a network interface to talk to other machines on the factory floor or the factory coordination unit; it may also use the file system to access a database for the manufacturing process.

#### Hardware/Software Co-Design 78.4

Hardware/software co-design refers to any methodology which takes into account both hardware and software during the design of an embedded computing system. When the hardware and software an designed together, the designer has more opportunities to optimize the system by making tradeous between the hardware and software components. Good system designers intuitively perform co-design but co-design methods are increasingly being embodied in computer-aided design (CAD) tools. We will discuss several aspects of co-design and co-design tools, including models of the design, co-simulation performance analysis, and various methods for architectural co-synthesis. We will conclude with a look at design methodologies that make use of these phases of co-design.

ing eml the des earliest ure all a perfor to make ents. O s, such a emente ters like tion is n it differi II applie ore detai are descri ved as spe of abstra size, etc. chart-like expression

Co-

ation is ar. modeling hardware re gate-leve of abstract ation of th be unacc e can gain rent levels ution can l am can be ing those 1 with the h ware. Thos of simulati at different in the ha e simulatic onents of

.3 Per

performa or meeting ent of any

#### Models

gning embedded computing systems, we make use of several different types of models at different in the design process. We need to model basic functionality. We must also capture nonfunctional ments: speed, weight, power consumption, manufacturing cost, etc.

the earliest stages of design, the task graph is an important modeling tool. The task graph does apture all aspects of functionality, but it does describe the various rates at which computations be performed and the expected degrees of parallelism available. This level of detail is often to make some important architectural decisions. A useful adjunct to the task graph are the mology description tables, which describe how processes can be implemented on the available monents. One of the technology description tables describes basic properties of the processing materials, such as cost and basic power dissipation. A separate table describes how the processes may make meters like precise power consumption) on a processing element of that type. The technology ription is more complex when ASICs can be used as processing elements, since many different at differing price/performance points can be designed for a given functionality, but the basic still applies.

more detailed description is given by either high-level language code (C, etc.) for software or redware description language code (VHDL, Verilog, etc.) for software components. These should not riewed as specifications—they are, in fact, quite detailed implementations. However, they do provide evel of abstraction above assembly language and gates and so can be valuable for analyzing performance, size, etc. The control-data flow graph (CDFG) is a typical representation of a high-level language: flowchart-like structure describes the program's control, while data flow graphs describe the behavior minimal expressions and basic blocks.

#### 84.2 Co-Simulation

mulation is an important tool for design verification. The simulation of a complete embedded system stalls modeling both the underlying hardware platform and the software executing on the CPUs. Some the hardware must be simulated at a very fine level of detail—for example, buses and I/O devices may quire gate-level simulation. On the other hand, the software can and should be executed at a higher rel of abstraction. While it would be possible to simulate software execution by running a gate-level mulation of the CPU and modeling the program as residing in the memory of the simulated CPU, this muld be unacceptably slow.

We can gain significant performance advantages by running different parts of the simulation at different levels of detail: elements of the hardware can be simulated in great detail, while software accution can be modeled much more directly. Basic functionality aspects of a high-level language togram can be simulated by compiling the software on the computer on which the simulation executes, allowing those parts of the program to run at the native computer speed. Aspects of the program which had with the hardware platform must interface to the section of the simulator which deals with the hardware. Those sections of the program are replaced by stubs which interface to the simulator. This had simulation is a multi-rate simulation system, since the hardware and software simulation sections at different rates: a single instruction in the software simulation will correspond to several clock order in the hardware simulation. The main jobs of the simulator are to keep the various sections the simulation synchronized and to manage communication between the hardware and software temponents of the simulation.

# 8.4.3 Performance Analysis

and for meeting deadlines, the analysis of the system to determine its speed of operation is an important dement of any co-design methodology. System performance—the time it takes to execute a particular

P5)

cies between processes.

lline first (EDF). This is a dynam priorities based on the impending rving the highest priority. Clearly deadlines. EDF can be shown at all deadlines will be met. Singler the system will be overload.

rigure 78.3, to create a task graph data to another. The sink processer which have no sk can run at its own rate. Data sources. Since the source and single use that information to eliminate ne. Narrowing the scope of processed.

emory footprint, since embedded OSs are also designed to be more the order of execution of processes to designed to have lower context for meeting deadlines. The kerne emory. A basic RTOS may have at rokernels often provide only basis may provide high-end operating gh-end RTOSs are POSIX (a Unit requires more hardware resources, a controller for a machine on the inchines on the factory floor or the a database for the manufacturing

s into account both hardware and set the hardware and software are the system by making tradeoff ners intuitively perform co-designaided design (CAD) tools. We will odels of the design, co-simulation nessis. We will conclude with a look

aspect of the system's functionality—clearly depends both on the software being executed a underlying hardware platform. While simulation is an important tool for performance analysis, it sufficient, since simulation does not determine the worst-case delays. Since the execution times or programs are data-dependent, it is necessary to give the simulation of the program the proper set of to observe worst-case delay. The number of possible input combinations makes it unlikely that on find those worst-case inputs without the sort of analysis that is at the heart of performance analysis.

In general, performance analysis must be done at several different levels of abstraction. Given a program, one can place an upper bound on the worst-case execution time of the program. However, since many embedded systems consist of multiple processes and device drivers, it is necessary to an how these programs interact with each other, a phase which makes use of the results of single-propression performance analysis.

Determining the worst-case execution time of a single program can be broken into two subprobled determining the longest execution path through the program and determining the execution time of program. Since there is at least a rough correlation between the number of operations and the acceptance of the instruction time, we can determine the longest execution path without detailed knowledge of the instructions being executed—the longest path depends primarily on the structure of conditionals and loo One way to find the longest path through the program is to model the program as a control-flow grand use network flow algorithms to solve the resulting system.

Once the longest path has been found, we need to look at the instructions executed along that put to determine the actual execution time. A simple model of the processor would assume that extinstruction has a fixed execution time, independent of other factors such as the data values being operation, surrounding instructions, or the path of execution. In fact, such simple models do not give adequate results for modern high-speed microprocessors. One problem is that in pipelined processors, the execution time of an instruction may depend on the sequence of instructions executed before it. An every greater cause of performance variations is caching, since the same instruction sequence can have variate execution times, depending on whether the code is in the cache. Since cache miss penalties are often so or 10X, the cost of mischaracterizing cache performance is significant. Assuming that the cache is never present gives a conservative estimate of worst-case execution time, but one that is so over-conservative that it distorts the entire design. Since the performance penalty for ignoring the cache is so large, it results in using a much faster, more expensive processor than is really necessary. The effects of caching can be taken into account during the path analysis of the program—path analysis can determine bound how often an instruction present in the cache.

There are two major effects which must be taken into account when analyzing multiple-process systems. The first is the effect of scheduling multiple processes and device drivers on a single CPU. This analysis is performed by a scheduling algorithm, which determines bounds on when programs can execute Ratemonotonic analysis is the simplest form of scheduling analysis—the utilization factor given be ratemonotonic analysis tells one an upper limit on the amount of active CPU time. However, if data dependencies between processes are known, or some knowledge of the arrival times of data is known then a more accurate performance estimate can be computed. If the system includes multiple processing elements, more sophisticated scheduling algorithms must be used, since the data arrival time for a process on one processing element may be determined by the time at which that datum is computed on another processing element.

The second effect which must be taken into account is interactions between processes in the cathe When several programs on a CPU share a cache, or when several processing elements share a second level cache, the cache state depends on the behavior of all the programs. For example, when one process is suspended by the operating system and another process starts running, that process may knock in first program out of the cache. When the first process resumes execution, it will initially run more slow an effect which cannot be taken into account by analyzing the programs independently. This analysiclearly depends in part on the system schedule, since the interactions between processes depends the order in which the processes execute. But the system scheduling analysis must also keep track of the cache.

curacy can of it, withoural sub-p

Hard

re/softwar puting sy ality. Co-s it concen s required most basic 8.4, this al or more A ngle progra to the CPU mance is do of the app application first probler e determinir the applicati an allocation d to determi equired to tra SIC. Since th In addition, vance, that cos element the ardware cost ic, co-synthes into the CP

eing executed

nance analysis,

xecution times of

the proper set of

t unlikely that or

ormance analysis

traction. Given a

he program, Ho

is necessary to ar

sults of single-pro

into two subproblems execution time of the erations and the acro owledge of the instructionalitionals and local as a control-flow grant

ecuted along that partial assume that each a values being operated is do not give adequated before it. An evoluted before it. So penalties are often 50 that the cache is never its so over-conservation che is so large, it result fects of caching can be determine bound how

ultiple-process systems agle CPU. This analysis programs can execute zation factor given by time. However, if data imes of data is known les multiple processin rrival time for a process computed on another

processes in the cache ments share a secondnple, when one process process may knock the itially run more slownendently. This analysis processes depends on t also keep track of the which parts of which programs are in the cache at the start of execution of each process. curacy can be obtained with a simple model which assumes that a program is either in the cache it, without considering individual instructions; higher accuracy comes from breaking a process ral sub-processes for analysis, each of which can have its own cache state.

### Hardware/Software Co-Synthesis

re/software co-synthesis tries to simultaneously design the hardware and software for an embednputing system, given design requirements such as performance as well as a description of the nality. Co-synthesis generally concentrates on architectural design rather than detailed component —it concentrates on determining such major factors as the number and types of processing is required and the ways in which software processes interact.

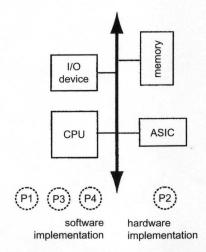

most basic style of co-synthesis is known as hardware/software partitioning. As shown in 78.4, this algorithm maps the given functionality onto a template architecture consisting of a CPU e or more ASICs communicating via the microprocessor bus. The functionality is usually specified agle program. The partitioning algorithm breaks that program into pieces and allocates pieces to the CPU or ASICs for execution. Hardware/software partitioning assumes that total system mance is dominated by a relatively small part of the application, so that implementing a small not the application in the ASIC leads to large performance gains. Less performance-critical sections application are relegated to the CPU.

the first problem to be solved is how to break the application program into pieces; common techniques de determining where I/O operations occur and concentrating on the basic blocks of inner loops. The application code is partitioned, various allocations of those components must be evaluated. In an allocation of program components to the CPU or ASICs, performance analysis techniques can used to determine the total system performance; performance analysis should take into account the required to transfer necessary data into the ASIC and to extract the results of the computation from ASIC. Since the total number of allocations is large, heuristics must be used to search the design the landition, the cost of the implementation must be determined. Since the CPU's cost is known advance, that cost is determined by the ASIC cost, which varies as to the amount of hardware required applement the desired function. High-level synthesis can be used to estimate both the performance hardware cost of an ASIC which will be synthesized from a portion of the application program.

asic, co-synthesis heuristics start from extreme initial solutions: We can either put all program compots into the CPU, creating an implementation which is minimal cost but probably does not meet

FIGURE 78.4 Hardware/software partitioning.

performance requirements, or put all program elements in the ASIC, which gives a maximal-performance maximal-expense implementation. Given this initial solution, heuristics select which program conton to move to the other side of the partition to either reduce hardware cost or increase performance, a More sophisticated heuristics try to construct a solution by estimating how critical a component overall system performance and choosing a CPU or ASIC implementation accordingly. Iterative ment strategies may move components across the partition boundary to improve the design.

However, many embedded systems do not strictly follow the one CPU, one bus, n ASIC architectures template. These more general architectures are known as distributed embedded systems. Technique designing distributed embedded systems rest on the foundations of hardware/software partitioning they are generally more complicated, since there are more free variables. For example, since the mand types of CPUs is not known in advance, the co-synthesis algorithm must select them. If the number of busses or other communication links is not known in advance, those must be selected as well. Unformately, these decisions are all closely related. For example, the number of CPUs and ASICs required depend on the system schedule. The system schedule, in turn, depends on the execution time of each of components on the available hardware elements. But those execution times depend on the process elements available, which is what we are trying to determine in the first place. Co-synthesis algorithm generally try to fix several designs and vary only one or a few, then check the results of a design decision the other parameters. For example, the algorithm may fix the hardware architecture and try to more processes to other processing elements to make more efficient use of the available hardware. Given that ne configuration of processes, it may then try to reduce the cost of the hardware by eliminating unuse processing elements or replacing a faster, more expensive processing element with a slower, cheaper one

Since the memory hierarchy is a significant contributor to overall system performance, the design of the caching system is an important aspect of distributed system co-synthesis. In a board-level system with existing microprocessors, the sizes of second-level caches is under designer control, even if the first-level cache is incorporated on the microprocessor and therefore fixed in size. In a single-chip embedded system, the designer has control over the sizes of all the caches. Co-synthesis can determine hardware elements such as the placement of caches in the hardware architecture and the size of each cache. It can also determine software attributes such as the placement of each program in the cache. The placement of a program in the cache is determined by the addresses used by the program—by relocating the program, the cache behavior of the program can be changed. Memory system design requires calculating the cache state when constructing the system schedule and using the cache state as one of the factors to determine how to modify the design.

## 78.4.5 Design Methodologies

A co-design methodology tries to take into account aspects of hardware and software during all phase of design. At some point in the design process, the hardware and software components are well-specified and can be designed relatively independently. But it is important to consider the characteristics of both the hardware and software components early in design. It is also important to properly test the system once the hardware and software components are assembled into a complete system.

Co-synthesis can be used as a design planning tool, even if it is not used to generate a complete system architectural design. Because co-synthesis can evaluate a large number of designs very quickly, it can determine the feasibility of a proposed system much faster than a human designer. This allows the designer to experiment with what-if scenarios, such as adding new features or speculating on the effects of lower component costs in the future. Many co-synthesis algorithms can be applied without having a complete program to use as a specification. If the system can be specified to the level of processes with some estimate of the computation time required for each process, then useful information about architectural feasibility can be generated by co-synthesis.

Co-simulation plays a major role once subsystem designs are available. It does not have to wait until all components are complete, since stubs may be created to provide minimal functionality for incomplete components. The ability to simulate the software before completing the hardware is a major boon to software development and can substantially reduce development time.

d R. Co

# 1.1 Inti

No invention in mortant to it in the 1960's be computer that management, it is same time, if devices that the semicondularkets from mobiles. Acros (C) chips, mosemblies. No electron baced tremen

th by CRC Pre

eration ha

gies, and

akthrough