# Interactive Distributed Embedded Systems

Robert Dick

http://robertdick.org/esds/ Office: 2417-E EECS Department of Electrical Engineering and Computer Science University of Michigan

Today's plan

Specification and modeling languages.

Comments on mini-project selection.

Example specification project.

Specification and modeling languages

## Short and fat vs. tall and thin

system level behavioral level register-transfer level logic level layout level transistor level

Specification and modeling languages

## Available resources – System-level

- General-purpose SW processors

- Digital signal processors (DSPs)

- Application-specific integrated circuits

- Dynamically reconfigurable hardware

- E.g., field-programmable gate arrays (FPGAs)

- Wireless communication channels

- Wires

Specification and modeling languages

## Available resources – High-level

- Simple arithmetic/logic units

- Multiplexers

- Registers

- Wires

Specification and modeling languages

# Specification language requirements

- Describe hardware (HW) and software (SW) requirements

- Specify constraints on design

- Indicate system-level building blocks

- To allow flexibility in synthesis, must be abstract

- Differentiate HW from SW only when necessary

- Concentrate on requirements, not implementation

- Make few assumptions about platform

Specification and modeling language Homework Introduction

Software oriented design representations

Hardware oriented design representations

Graph based design representations

Page 1970 descriptions

# Software oriented design representations

- ANSI-C

- SystemC

- Other SW language-based

Robert

nteractive Distributed Embedded Systems

Specification and modeling languages Homework Software oriented design representations Hardware oriented design representation Graph based design representations Resource descriptions

## SystemC

#### Advantages

- Support from big players

- Synopsys, Cadence, ARM, Red Hat, Ericsson, Fujitsu, Infineon Technologies AG, Sony Corp., STMicroelectronics, and Texas Instruments

- Familiar for SW engineers

## Disadvantages

- Extension of SW language

- Not designed for HW from the start

- Compiler available for limited number of SW processors

- New

Robert D

Interactive Distributed Embedded System

Specification and modeling languages Homework Software oriented design representations Hardware oriented design representations Graph based design representations Resource descriptions

#### Hardware oriented design representations

- VHDL

- Verilog

- Esterel

Specification and modeling la Ho oftware oriented design representations lardware oriented design representations raph based design representations

## **ANSI-C**

#### Advantages

- Huge code base

- Many experienced programmers

- Efficient means of SW implementation

- Good compilers for many SW processors

#### Disadvantages

- Little implementation flexibility

- Strongly SW oriented

- Makes many assumptions about platform

- Poor support for fine-scale HW synchronization

Rol

Interactive Distributed Embedded Systems

Specification and modeling languages

Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

Resource descriptions

## Other SW language-based

- Numerous competitors

- Numerous languages

- $\bullet$  ANSI-C, C++, and Java are most popular starting points

- In the end, few can survive

- SystemC has broad support

Robert D

Interactive Distributed Embedded System

Specification and modeling langua, Homew Software oriented design representations Hardware oriented design representations Graph based design representations Resource descriptions

## **VHDL**

#### Advantages

- Supports abstract data types

- System-level modeling supported

- Better support for test harness design

#### Disadvantages

- Requires extensions to easily operate at the gate-level

- Difficult to learn

- Slow to code

Robert

Interactive Distributed Embedded Systems

Robert Dick

Interactive Distributed Embedded Systems

Specification and modeling languages

Introduction

Software oriented design representations

Hardware oriented design representations

Graph based design representations

# Verilog vs. VHDL

Software oriented design representations Hardware oriented design representations Graph based design representations Resource descriptions

# Verilog

#### Advantages

- Easy to learn

- Easy for small designs

#### Disadvantages

- Not designed to handle large designs

- Not designed for system-level

generated even parity, carry and borrow • 5 / 9 Verilog users completed

• March 1995, Synopsys Users Group meeting

• 0 / 5 VHDL users competed

Does this mean that Verilog is better?

Maybe, but maybe it only means that Verilog is easier to use for simple designs.

• Create a gate netlist for the fastest fully synchronous loadable

9-bit increment-by-3 decrement-by-5 up/down counter that

Robert [

Interactive Distributed Embedded Systems

18

Interactive Distributed Embedded Systems

Specification and modeling languages Homework Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

Persource descriptions

#### Esterel

- Easily allows synchronization among parallel tasks

- Works above RTL

- Doesn't require explicit enumeration of all states and transitions

- Recently extended for specifying datapaths and flexible clocking schemes

- Amenable to theorem proving

- Translation to RTL or C possible

- Commercialized by Esterel Technologies

Specification and modeling languages

Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

Resource descriptions

# Graph based design representations

- Dataflow graph (DFG)

- Synchronous dataflow graph (SDFG)

- Control flow graph (CFG)

- Control dataflow graph (CDFG)

- Finite state machine (FSM)

- Petri net

- Periodic vs. aperiodic

- Real-time vs. best effort

- Discrete vs. continuous timing

- Example from research

Dec

Robert Dick

teractive Distributed Embedded Systems

pecification and modeling languages

Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

Resource descriptions

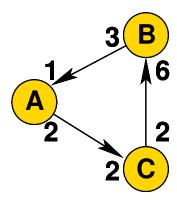

# Dataflow graph (DFG)

- Nodes are tasks

- Edges are data dependencies

- Edges have communication quantities

- Used for digital signal processing (DSP)

- Often acyclic when real-time

- Can be cyclic when best-effort

Specification and modeling languages Homework Software oriented design representations Hardware oriented design representation Graph based design representations Resource descriptions

# Synchronous dataflow graph (SDFG)

Robe

Specification and modeling languages

Introduction Software oriented design representations Hardware oriented design representation Graph based design representations

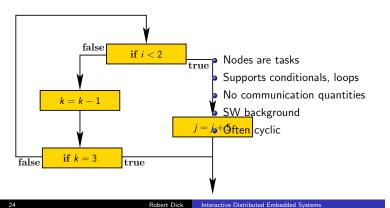

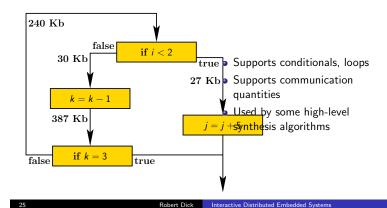

## Control flow graph (CFG)

Control dataflow graph (CDFG)

troduction

oftware oriented design representations

ardware oriented design representations

caph based design representations

Specification and modeling languages Homework Software oriented design representations Hardware oriented design representation Graph based design representations

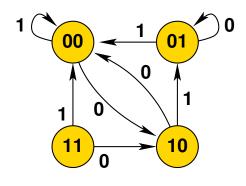

## Finite state machine (FSM)

Robert D

Interactive Distributed Embedded Systems

Specification and modeling languages Homework Introduction

Software oriented design representation

Hardware oriented design representation

Graph based design representations

Resource descriptions

# Finite state machine (FSM)

|         | input |    |

|---------|-------|----|

|         | 0     | 1  |

| 00      | 10    | 00 |

| 01      | 01    | 00 |

| 10      | 00    | 01 |

| 11      | 10    | 00 |

| current | next  |    |

- Normally used at lower levels

- Difficult to represent independent behavior

- State explosion

- No built-in representation for data flow

- Extensions have been proposed

- Extensions represent SW, e.g., co-design finite state machines (CFSMs)

Introduction

Software oriented design representation

Hardware oriented design representation

Graph based design representations

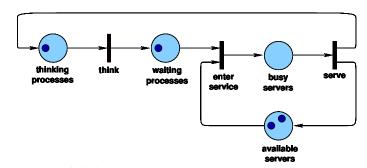

## Petri net

- Graph composed of places, transitions, and arcs

- Tokens are produced and consumed

- Useful model for asynchronous and stochastic processes

- Places can have priorities

- Not well-suited for representing dataflow systems

- Timing analysis quite difficult

- Large flat graphs difficult to understand

Specification and modeling languages

Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

## Petri net

M/D/3/2: Markov arrival, deterministic service delay, From A. Zimmermann's token game demonstration.

Robert I

Specification and modeling languages

Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

## Periodic graphs

- Some system specifications contain periodic graphs

- Can guarantee scheduling validity by scheduling to the least common multiple of periods

- Can also meet aperiodic specifications, however, resources will sometimes be idle

Robert [

Interactive Distributed Embedded Systems

Specification and modeling languages Homework Software oriented design representations

Hardware oriented design representation

Graph based design representations

Resource descriptions

## Aperiodic graphs

- No precise periods imposed on task execution

- Useful for representing reactive systems

- Difficult to guarantee hard deadlines in such systems

- Possible if minimum inter-arrival time known

Robert Dick

Interactive Distributed Embedded System

Specification and modeling languages

Software oriented design representations Hardware oriented design representations Graph based design representations Resource descriptions

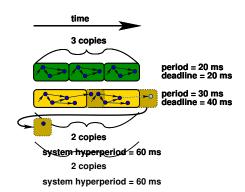

#### Aperiodic to periodic

Can design periodic specifications that meet requirements posed by aperiodic specifications

• Some resources will be wasted

#### Example:

- At most one aperiodic task can arrive every 50 ms

- It must complete execution within 100 ms of its arrival time

Specification and modeling languages Homework ntroduction

oftware oriented design representations

lardware oriented design representations

fraph based design representations

## Periodic graphs

Interactive Distributed Embedded Systems

Specification and modeling language Homework Introduction

Software oriented design representatio

Hardware oriented design representation

Graph based design representations

Resource descriptions

## Periodic vs. aperiodic

#### Periodic applications

- Power electronics

- Transportation applications

- Engine controllers

- Brake controllers

- Many multimedia applications

- Video frame rate

- Audio sample rate

- Many digital signal processing (DSP) applications

However, devices which react to unpredictable external stimuli have aperiodic behavior

Many applications contain periodic and aperiodic components

Robe

Interactive Distributed Embedded Systems

Specification and modeling languages Homework Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

Procures descriptions

## Aperiodic to periodic

- Can easily build a periodic representation with a deadline and period of 5 ms

- Problem, requires a 50 ms execution time when 100 ms should be sufficient

- Can use overlapping graphs to allow an increase in execution time

- Parallelism required

The main problem with representing aperiodic problems with periodic representations is that the tradeoff between deadline and period must be made at the time of synthesis

Robert Di

Interactive Distributed Embedded Systems

Robert Dick

Interactive Distributed Embedded Systems

Specification and modeling languages

Homework

Introduction

Software oriented design representations

Hardware oriented design representations

Graph based design representations

# Discrete vs. continuous timing

Software oriented design representations Hardware oriented design representations Graph based design representations Resource descriptions

## Real-time vs. best effort

- Why make decisions about system implementation statically?

- Allows easy timing analysis, hard real-time guarantees

- If a system doesn't have hard real-time deadlines, resources can be more efficiently used by making late, dynamic decisions

- Can combine real-time and best-effort portions within the same specification

- Reserve time slots

- Take advantage of slack when tasks complete sooner than their worst-case finish times

System-level: continuous

- Operations are not small integer multiples of the clock cycle High-level: discrete

- Operations are small integer multiples of the clock cycle Implications:

- System-level scheduling is more complicated...

- ...however, high-level also very difficult.

Robert Dick Interactive Distributed Embedded Syste

Specification and modeling languages Homework Introduction

Software oriented design representations

Hardware oriented design representations

Graph based design representations

Resource descriptions

# Processing resource description

- Often table-based

- Price, area

- For each task

- Execution time

- Power consumption

- Preemption cost

- etc.

- etc.

Similar characterization for communication resources Wise to use process-based

Specification and modeling languages Homework Introduction

Software oriented design representations

Hardware oriented design representation

Graph based design representations

Resource descriptions

## Communication resource description

- Can use bus-bridge based models for distributed systems

- Wireless models

- etc.

- However, in the future, it will become increasingly important to base SOC communication model on process parameters

Robert Dick

nteractive Distributed Embedded System

pecification and modeling languages Homework Introduction

Software oriented design representations

Hardware oriented design representations

Graph based design representations

Resource descriptions

# Example from research

## Data-flow graphs

- Multirate

- Hard real-time

- Some aperiodic hard real-time tasks

- May have best-effort tasks

System-level representations summary

- No single representation has been decided upon

- Software-based representations becoming more popular

- System-level representations will become more important

- This is still an active area of research

Rober

Interactive Distributed Embedded Systems

Robert Dic

nteractive Distributed Embedded System

Notes on clustering and partitioning

## Interesting future direction

#### • Interdependence with architecture

- Heterogeneity's impact on partitioning

- Applications to grid computing

- Dynamic partitioning

# Open problem

- Can specification be so simple for some embedded application domains that application experts who are not computer engineers easily do it?

- What HCI, compiler, and synthesis support is required?

## Continue study of topics of interest

- Due before class on 16 Jan.

- Revise your 14 Jan report based on my feedback in class on Monday and into structure shown in examples on website.

- I will use this revised report to provide additional feedback.

## Project proposals

- Due before class on 21 Jan.

- Written project proposals with clear plan for checkpoint 1 and checkpoint 2.

- Follow style in example on website.

- Clearly describe and cite closest related work.

- Identify infrastructure you will use or build upon.

- Indicate new research problems that must be solved.

- Indicate what will be completed by each of the checkpoints, and by the end of the course. Some revision of checkpoint 2 and the final results are expected.

#### Reading assignment

- Due before class on 16 Jan.

- One-paragraph written summary.

- Fang-Jing Wu, Yu-Fen Kao, and Yu-Chee Tseng. From wireless sensor networks towards cyber physical systems. Pervasive and Mobile Computing, 7:398-409, July 2011.

## **Upcoming lectures**

- Embedded system design optimization.

- Embedded system research communities and review process.